有望改变 AI 半导体规则,消息称三星电子年内将推出 HBM 三维封装技术 SAINT-D

IT之家 6 月 18 日消息,据韩媒《韩国经济日报》报道,三星电子将于年内推出可将 HBM 内存与处理器芯片 3D 集成的 SAINT-D 技术。

报道同时指出,在今年发布后,三星有望于明年推出的 HBM4 内存中正式应用 SAINT(IT之家注:即 Samsung Advanced INterconnect Technology 的简写)-D 技术。

SAINT-D 是三星电子的一项 3DIC 先进封装技术,旨在垂直集成逻辑裸片和 DRAM 内存裸片。报道称该技术的具体实现方式是在处理器和 HBM 芯片间建立硅中介层。

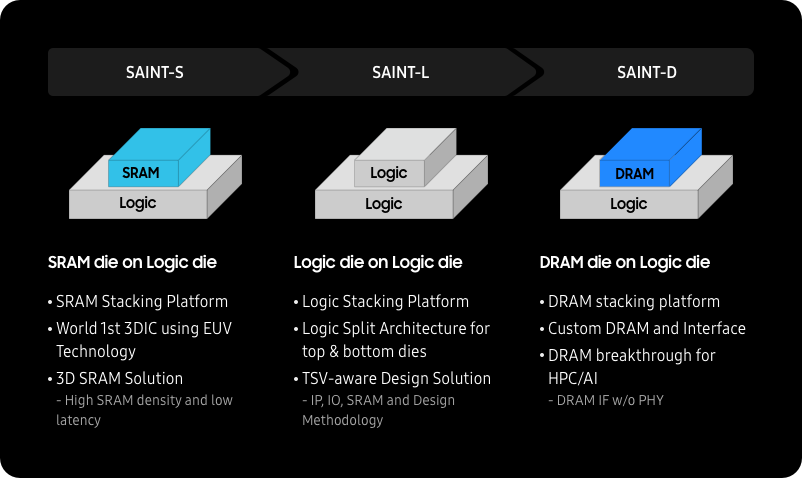

▲ 三星电子 SAINT 先进封装技术家族

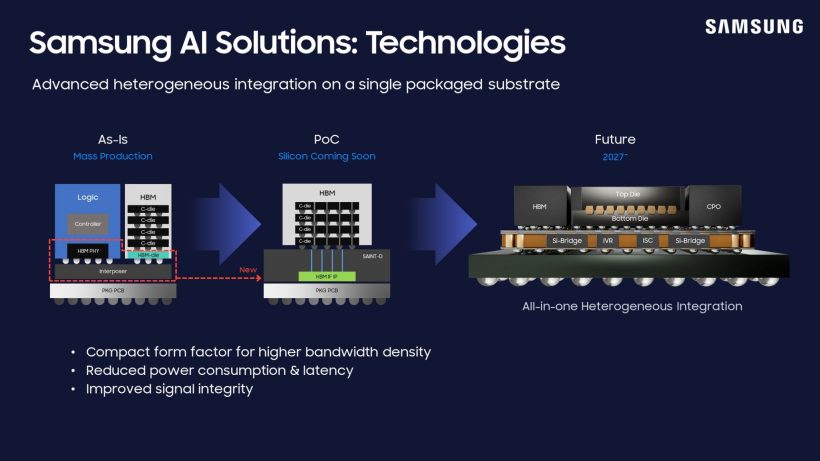

三星电子近期在三星代工论坛 2024 北美场上表示,其 SAINT-D 技术目前正处于概念验证阶段。

▲ 三星 AI 解决方案,中即 SAINT-D 技术

韩媒表示,SAINT-D 技术有望改变 AI 半导体领域的游戏规则:

目前 HBM 内存与处理器之间采用 2.5D 封装连接,两者之间存在一定距离,不仅引入了更大传输延迟,同时还影响了电信号质量、提升了数据移动功耗。

而 SAINT-D 技术将处理器和 HBM 内存的距离降到更低,有利于 AI 加速器芯片进一步释放性能潜力。

对于三星电子整体而言,由于可提供从先进节点代工、HBM 内存生产到整体封装集成的全流程“交钥匙”服务,SAINT-D 的应用也可带动 HBM 和代工业务的发展。

根据市场研究机构 MGI 的数据,SAINT-D 等先进封装市场的规模将从 2023 年的 345 亿美元成长至 800 亿美元。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码