非传统MOSFET方案提高功率CMOS器件功效的方法

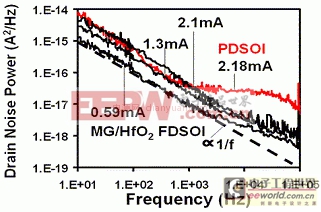

图9:与PDSOI器件相比,FD-SOI 器件显示出更低的噪音。

应变硅与增强传输特性

通过改善短沟道静电的影响,降低了漏电、可变性及待机功耗。在某种程度上,它甚至改进了传输特性。然而, 要充分地降低动态功耗,而不必对漏电和性能作出折衷,就需要进一步增强传输特性。

由于动态功耗的二次方程式取决于Vdd (CVdd2F), 调整电源电压是降低动态功率的最有效的方法。然而,如果门限电压并没有降低, 那么,Vdd的减少会导致晶体管中载流子密度(Qi)的大量损耗。

Qi(max) ~ Cox (Vdd-VT)

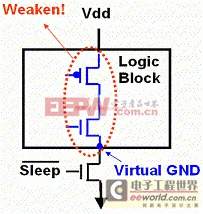

由于源/漏漏电呈指数地依赖于VT(图2), 要调整VT就变得十分受到限制。此外,Cox的增加受到Tox的限制, 这一点最终受到门漏电和电介质可靠性的限制。 当晶体管被堆叠以减少漏电时,一个类似的问题又出现了(图10)。在逻辑模块中的堆叠器件要减少其最大门栅过驱动的虚拟节点(Vdd‘-VT),因此,它 们会随着堆叠的增加变得更加弱。

图10:晶体管堆叠对于实现“休眠”晶体管和电源门控技术已很常见。

要恢复相同的电流(I=Qi速率),载流子速率(或迁移率)必须得到增加以弥补Qi损耗。这正是迁移率随应变硅的优越而得到增强之处。

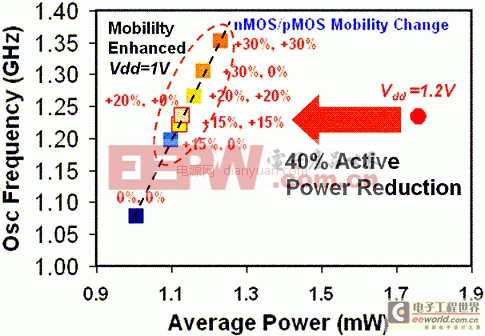

随着英特尔宣布,把应力衬底材料和SiGe源/漏的结合进入90nm 技术节点,针对不同工艺的应变硅已应用到产品之中,被集成以增强他们的CMOS器件[4]。此外,人们还研究了从双压力衬底到衬低应变硅的许多其它的方 法。推动晶体管性能的根本目标是相同的:实质性地增强迁移率,我们能在维持电路性能的同时,为降低动态功耗,而对驱动电流进行折衷(图11)。

图11: 振荡器电路模拟表明:在保持频率性能的同时提高迁移率,通过把Vdd从1.2V 降到1V,可以减低平均功耗。

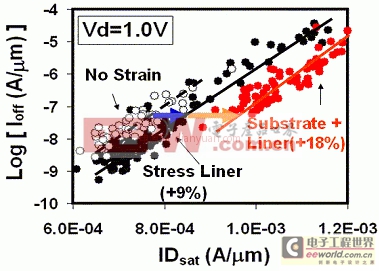

这就意味着提高迁移率?传统的高性能晶体管的发展推动力?也开始向低功耗管理这个前沿转移,因此,要研究获得更高迁移率的缩放路径。通过工艺技术把现有各种应力材料的优势结合起来并加以增强,是进一步提高性能的自然方法(图12, 13) [5]。最终,除了应变硅外,可能还需要具有更高迁移率的非硅材料,从而引领工艺及设计工程师努力开发新工艺并解决各种设计复杂性问题。

图12:直接制作在在绝缘体上的应变硅(衬底应变)与嵌入式SiGe源?漏及衬底应力材料的结合,可以实现混合应变PMOSFET。

图13:由应力衬低结合的绝缘体(衬底应变硅)上直接制作的应变硅增强了的NMOSFET性能。

提高迁移率终于获得了成功,Lg和沟道迁移率的提升加速了晶体管沟道阻抗(Rch)的降低,而寄生源/漏和接触电阻(Rsd)要以更慢的速度降低。由于寄生参数导致越来越多的电压 降,增加Rsd/Rch比率会导致逐渐抵消所增强的晶体管性能,尽管迁移率增加(图14)[6]。这就意味着,要把寄生电阻急剧降

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码