采用AD9913的低相噪频率合成器设计

相噪分析

器件选型上,100MHz参考源采用恒温晶体振器,相位噪声设计值应不低于-155dBc/Hz/10k,本振由阶跃二极管倍频电路实现,DDS采用AD9913,鉴相/分频器则采用HMC700。

其中,DDS用100MHz时钟激励输出23.88~25MHz时,其相位噪声小于-145dBc/Hz/10k,经混频除4后相位噪声可达-155dBc/Hz/10k,鉴相/分频器的本底相位噪声值为-225dBc/Hz。

由公式(2)可估算出近载频10k时(M=28,N=40),系统闭环输出相位噪声为:

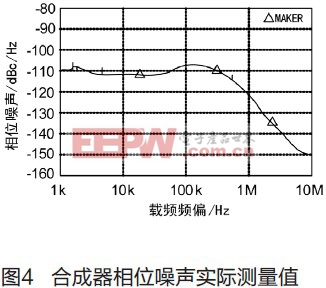

实际测量如图4所示,合成器的相位噪声测量结果与计算基本吻合。

杂散抑制

本方案中,合成器杂散的主要来源有以下三个部分。

(1)DDS(AD9913)产生的杂散。通过在DDS输出端的带通滤波器将DDS产生的杂散滤除。

(2)混频产生组合频率分量。取样本振与VCO输出混频后,除得到有用的中频信号外,还会产生大量无用的组合分量,这些无用分量如果不加以抑制,会泄漏到合成器输出端,形成杂散。设计时通过方向性较强的放大器级联提供反向隔离,同时在混频器后面设计一个带通滤波器,滤除混频后的杂散信号,并在电路上进行良好的屏蔽,以保证系统指标要求。

(3)鉴相频率泄漏。鉴相频率来自分频产生的矩形脉冲,包含着丰富的混波分量,电路中需通过环路滤波器进行抑制,为达到更好阻带特性,可在环路中附加一个LC低通滤波器来实现。

结束语

本文介绍了一种用于超短波通信设备的C波段低相噪频率合成器,并详细分析了其相位噪声、杂散抑制性能。在调试过程中,作环路滤波器所产生的噪声对试验结果有较大影响,使得环路转折频率附近有底噪声干扰现象,通过改进环路滤波器的参数后解决干扰。该合成器已投入工程中应用,实用效果较好。

参考文献:

[1] AD9913 Datasheet[Z].Analog Device Corp.

[2] HMC440 Datasheet[Z].HITTITE Corp.

[3] 方立军.一种C波段低相噪锁相频率合成器[J].现代电子,2001,73,(4):41-45

[4] 赵海清.一种新颖的频率合成器捷变频方案[J].电讯技术,2002,42,(4):5-8

[5] 赵彦芬.频率合成器环路滤波器的设计[J].无线电工程,2006,36,(4):39-41

[6] 张广显,白锡巍.阶跃二极管高阶倍频器研制[J].半导体情报,2000,37,(2):50-52

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码