采用AD9913的低相噪频率合成器设计

根据相位噪声最优原则,环路滤波器的转折频率ωn应取在式(2)、(3)的交点,其闭环特性为:在环路带宽内,系统输出的相位噪声主要取决于参考信号和数字鉴相器基底噪声,在环路带宽外,相位噪声则主要由VCO决定。

C波段混频锁相合成器设计

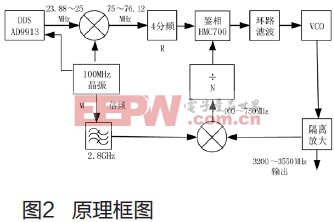

原理框图

混频锁相合成器由DDS电路、混频电路、压控振荡器、鉴相器、环路滤波器、程序分频器等基本电路构成。具体原理框图见图2。

主锁相环中,3200~3550MHz的输出信号通过取样本振下变频至400~750MHz,分频后与参考信号鉴相。取样本振(2.8GHz)由100MHz高稳晶振经倍频滤波后产生。

本方案中,环路滤波器按500kHz带宽设计环路参数,因此在近载频处,对相位噪声有直接影响的因素是参考信号、倍频噪声和鉴相/分频器本底噪声,在远载频处,相位噪声则主要受压控振荡器的开环特性决定。

AD9913介绍

AD9913是美国ANALOG DEVICES公司生产的新型低功耗直接数字频率合成器(DDS),它采用先进的DDS技术,结合内部高速高性能的D/A转换器和比较器,可编程参考时钟倍乘器形成可编程、可灵活使用的频率合成功能。AD9913产生高稳定、频率相幅可编程的正弦波,可作为信号源广泛应用于通信工程、雷达仪器仪表、高速计算机及导航系统中。

AD9913具有以下重要特性:100MHz模拟输出和0.058Hz或更高的频率分辨率;相位噪声≤-135dBc的每Hz@1kHz偏移(DAC输出);出色的动态性能:≥80dB的SFDR@100MHz(±100kHz偏移);自动线性扫频能力;极低功耗(50mw,1.8V电源);可选的PLL REF_CLK倍频,最高工作时钟可达250MHz。

AD9913内部集成了DDS模块、10位DAC、REF_CLK输入电路、时序和逻辑控制电路以及对外I/O接口模块等,内部功能方框图见图3。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码