基于FPGA的SoC原型验证的设计与实现

(4)Scatter文件部分。scatter文件是用来描述删连接器生成映像文件时需要的地址映射信息和加载域信息。

下面以UART模块为例,在此框架下根据其接口编写相应的测试程序。

验证计划:通过待验UART与PC进行通信来验证其功能是否正确,主要验证的功能点有:1)寄存器读写;2)三种工作模式普通模式、自流控模式、LoopBack模式;3)奇偶校验;4)波特率;5)FIFO触发级。

测试程序:根据上边的功能点可以划分两个测试的基本的函数,一个是寄存器读写的测试函数UART_RWTst(),还有一个就是UART工作配置函数UART_Config(),这个函数提供一个接口,通过这个接口可以配置UART的工作模式、奇偶校验方式、波特率大小、FIFO触发级。在更高层的测试应用程序中调用配置程序,变化配置参数,使其与PC进行收发数据,然后查看或比对数据,判别其功能是否正确。测试程序文件结构如图5所示。

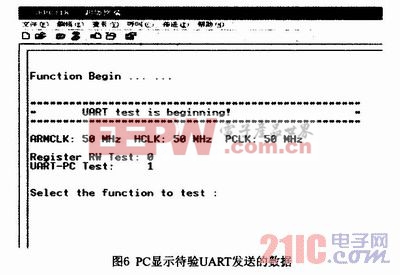

验证结果:当待验UART向PC发送数据时,在PC的超级终端会显示这些数据,UART功能验证结果可通过观测或数据比对来判断,如图6所示。

4 结论

同样的测试激励程序在此原型平台的执行速度要比SDV(Software driven verification)平台快4~6个数量级。本验证平台的搭建过程中对其进行了形式验证和时序分析,大大减少了在原型设计中由于FPGA实现而导致的错误。本平台的软件测试程序具有接口简单、易调试、可重用性好等特点,笔者在此原型平台下完成了部分模块的验证,有效地提高了验证效率,缩短了项目的开发周期,加大了流片成功率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码