基于FPGA的SoC原型验证的设计与实现

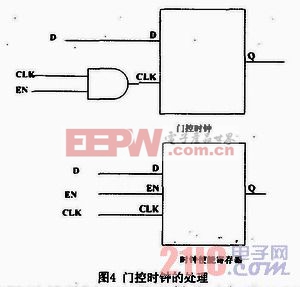

为了减少功耗,SoC设计中使用了门控时钟(clockgating),如图4所示,对于FPGA来说这种门控时钟容易产生毛刺,导致数据不正确,所以在FPGA设计中要使用时钟使能寄存器代替门控时钟。

2.2.2 设计综合

综合是将较高级抽象层次的描述转换成较低层次描述,在这里就是把HDL程序转化成标准的门级结构网表。本设计采用的EDA工具是Sy-nopsys公司的Synplify,将SoC的各个模块分别进行综合,综合时要加约束文件和Altera公司的相应器件的库文件,产生一个FPGA网表文件。

2.2.3 等价性检查

形式验证(Formal Verification)主要用来在覆盖所有可能输入情况下,检查是否与给定的规范一致。等价性检查(equivalence check-ing)是形式验证中的一部分,它主要是检查两个门级网表(gate-level netlisf)之间是否一致,保证网表处理后不会改变电路的功能,或者检查RTL和门级网表之间是否一致,保证网表能正确地实现RTL代码所描述的功能,或者检查RTL间是否一致,保证两种RTL描述逻辑一致。这种方法主要是用来寻找实现(Implementation Design)中的缺陷,而不是设计中的缺陷。由于芯片开发中,设计代码将不断的更改,都需要

更新FPGA的镜像文件,这样在频繁的镜像制作过程中,可能会因为环境和设计的更改引出许多实现过程中的错误,而本文为了减少这些错误,采用的Synopsys公司的Formality工具,主要用于检查网标和RTL间是否一致,把RTL设计作为Reference Design,而把网标作为Imple-mentation Design,在进行等价性检查时要加入Altera器件综合过程中需要的相关库文件。

2.2.4 设计整合和布局布线

把多个设计文件转换合并到一个设计库文件中,并把整合后的设计输入到Altera公司的QuartuslI工具,将综合过的网表中的逻辑门映射到FPGA的内部资源中,如ALUT等。

布局是指从映射取出定义的逻辑和输入输出块,并把它们分配到FPGA内部的物理位置,布线是指利用自动布线软件使用布线资源选择路径试着完成所有的逻辑连接。

2.2.5 时序分析

在设计实现过程中,在映射后需要对一个设计的实际功能块的延时和估计的布线延时进行时序分析。而在布局布线后,也要对实际布局布线的功能块延时和实际布线延时进行时序分析。时序分析不仅可以检查出我们代码设计中的时序问题,还可以检查出由于布局布线产生的时序问题。在本设计中用Altera公司的TimeQuest来进行时序分析,通过对原型设计增加时序约束,提高了工作主频和减少了关键路径的延时。在设计中经常存在时序违约的情况,这时需要查看违约的关键路径,然后查找原因,进行修改后再进行时序分析,重复整个过程直到满足要求。

2.2.6 镜像文件的生成和下载配置

QuartusII经过整合、布局布线等一系列操作后,最终会生成一个配置FPGA的位流文件(.sof洛式),然后利用QuartusII的Programmer工具,通过USB Blaster下载到FPGA,此时FPGA实现了原SoC设计的功能,原型验证环境搭建完成。

3 FPGA原型验证测试激励的设计

测试程序在FPGA基原型验证中起至关重要的作用,现在的SoC设计很多都采用IP复用的方式,本文所设计出的测试程序有可重用性好、功能覆盖率高和调试简易等特点。

测试程序的基本框架如图5所示,具体模块的测试程序只需要根据框架所提供的接口进行编写相应的测试程序即可,代码主要由以下四部分组成:

(1)系统启动部分。主要包含系统的异常向量表和系统启动后设置ARM内核的配置程序,如各种模式下的堆栈设置、开启或关闭FIR和IRQ、设定中断向量表等,在Boot_gfd.s中提供了跳到测试程序的接口。

(2)模块测试部分。在此部分根据各个模块的功能,编写相应的测试函数,系统在执行时会调用这些函数,完成我们各个模块的功能测试。

(3)头文件部分。为了方便代码的编写和理解,在tyoedef.h文件中对系统的数据类型做了重新定义并包含了部分公用函数的宏定义。一个SoC系统中拥有大量的寄存器,在本设计中用Register.h文件来存放这些寄存器地址的宏定义。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码