基于FPGA的SoC原型验证的设计与实现

2.1 FPGA原型验证平台的硬件环境设计

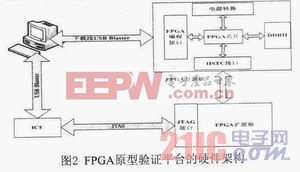

FPGA原型验证平台的硬件设计应该考虑FPGA的逻缉资源、应用资源、扩展能力、PCB信号质量、调试难度、组态和成本等方面的因素。本原型系统设计的FPGA开发板采用的是Terasic公司的DE3开发板,其FPGA芯片是StratixIII EP3SL340,扩展板是根据SoC整体验证方案而设计的PCB板。FPGA原型验证平台的硬件架构如图2所示,为了使FPGA的调试性能增强,该平台加入了ICE在线调试器,它可以让验证人员和软件开发人员观察到ARM内核和设计中各个寄存器的状态信息,并且可以进行单步运行、在线调试等。

2.2 FPGA原型验证平台的软件环境设计

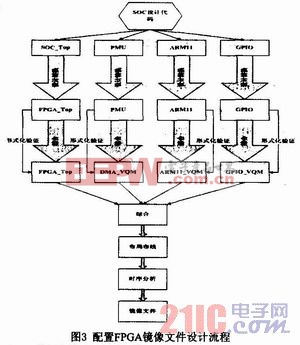

SoC芯片采用的是ASIC工艺流程,ASIC和FPGA在实现结构上是不同的,AISC通常使用综合工具将RTL级代码映射到芯片制造厂提供的标准单元上。这些标准单元包括完成逻辑功能的与非门、非门、或非门等基本门单元和完成存储功能的各类触发器、锁存器,以及其它的宏单元。而FPGA器件为了实现可编程功能,通常使用查找表结构实现电路的逻辑功能。本文原型设计流程如图3所示,在图示中仅是将部分模块列出,如PMU和GPIO。

2.2.1 设计代码的转换

虽然FPGA和ASIC所用资源和实现方式不同,但在进行原型设计中需要遵循的一个原则就是“尊重原设计”。在FPGA现有资源情况下实现SoC时,尽可能地少改动原SoC设计,在此基础上需要对原设计做如下转换:

(1)存储模块。存储单元是必须进行代码转换的,ASIC中的存储单元通常用代工厂所提供的Memory Compiler来定制。如果直接将ASIC代码中的存储单元作为FPGA的输入,通常综合器是综合不出来的,即使能综合出来,也要花费很长时间,并且资源消耗多、性能不好。而FPGA厂商一般提供经过验证并优化的存储单元,因此存储单元要进行代码转换。在设计里用FPGA的RAM宏单元来替换ESRAM,SoC芯片里面的DDR PHY是模拟的模块,此要替换成Altera公司的PHY的IP核。

(2)时钟和门控。数字电路中,时钟是整个电路最重要、最特殊的信号。在ASIC中,用布局布线工具来放置时钟树,利用代工厂提供的PLL进行时钟设计。而FPGA中通常已经配置一定数量的PLL宏单元,并有针对时钟优化的全局时钟网络,一般是经过FPGA的特定全局时钟管脚进入FPGA内部,后经过全局时钟BUF适配到全局时钟网络,这样的时钟网络可以保证相同的时钟沿到达芯片内部每一个触发器的延迟时间差异可以忽略不计,因此时钟单元需要采用FPGA的PLL宏单元和专门的时钟布线资源来替换。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码