善用预偏置晶体管 省板省料!

本文总结了预偏置晶体管的定义、作用、电路分析及设计要点,强调其在减小PCB尺寸、降低元件数量方面的优势,并提醒合理选择以匹配微控制器与负载。

什么是预偏置( pre-biased )晶体管?

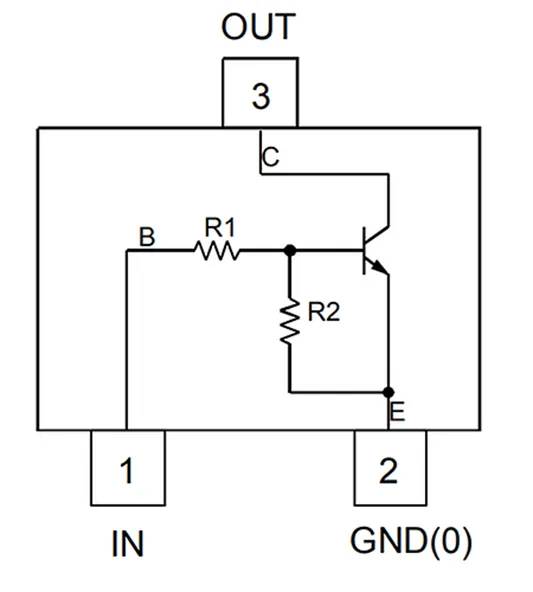

预偏置晶体管是在制造过程中集成了偏置电阻的晶体管。这种设计具有成本效益,集成的元件节省了印刷电路板(pcb)的成本,并减少了物料清单(BOM)中的项目数量。一个典型的产品是 Diodes 的 DDTD113ZC-7-F NPN 晶体管,采用 SOT - 23 - 3 封装,如图 1 所示。这种预偏置晶体管包括一个 1 千欧的串联限流电阻,以及一个与基极 - 发射极结并联的 10 千欧关断电阻。

图 1:DDTD113ZC-7-F: 带有串联电阻 R1 和基极到发射极电阻 R2 的预偏置晶体管

预偏置晶体管在电路中如何使用?

预偏置晶体管设计用于与微控制器等数字逻辑直接连接,从而无需额外的辅助电阻。这样可以实现紧凑的 PCB设计,并减少元件数量,因为三个传统元件被集成到了单个封装中。

预偏置晶体管中每个电阻的作用是什么?

典型的预偏置晶体管包含两个内部电阻。按功能可将它们分类如下:

串联限流电阻 :与 LED电路中的串联电阻类似,该串联电阻用于限制基极电流。

关断(分流)电阻 :与晶体管基极 - 发射极结并联的这个电阻有助于晶体管关断。当输入串联电阻断开时,例如微控制器 I/O在启动时设置为高阻抗或处于超低功耗(ULP)模式时,它提供一个泄漏路径,使基极保持在零伏。这个关断电阻还有助于降低ICE(集电极 - 发射极)间的泄漏电流。

市场上有多种预偏置的 NPN 和 PNP 晶体管可供选择。设计人员可以选择具有最合适的串联电阻和关断电阻的产品,以匹配其应用需求。

数字(开关)电路中强制 β 操作的必备晶体管理论

晶体管的特性之一是其直流电流增益(β),它被定义为集电极电流与基极电流之比。对于在其线性区域工作的晶体管,这是模拟设计中的一个重要指标。

在数字(开关)设计中应避免线性操作。相反,我们将重点关注强制 β。通过这种设计技术,我们有意使晶体管过驱动,以确保其完全饱和,从而特意避开线性区域。作为初步估计,我们假设强制 β 为 10,但要注意,强制 β 明显低于线性 β。

预偏置晶体管电路的电路分析

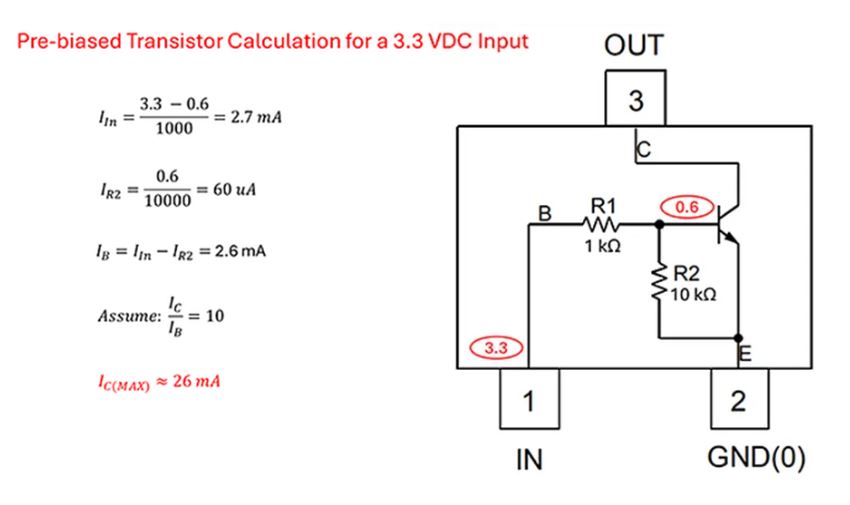

图 2 展示了Diodes DDTD113ZC - 7 - F 的电路分析。该晶体管的 R1 值为 1 千欧,R2 值为 10 千欧,并且具有高增益。

在这个应用中,晶体管由 3.3 伏直流逻辑信号驱动:

R1 串联电阻将输入电流限制在 2.7 毫安。这是一个相对较低的驱动电平,大多数微控制器都能轻松提供。然而,正如在下一个技术小贴士中所探讨的,这个值可能仍然过高。

关断电阻消耗一小部分输入电流。根据所选预偏置晶体管的 R1 与 R2的比率,这对电路计算可能重要,也可能不重要。

基极电流计算为输入电流减去关断电阻电流。

假设处于强制 β 条件下,最大集电极电流计算为基极电流的十倍。请注意,这是一个保守估计,用于确保晶体管进入饱和状态。您可以通过测试设计中的极端情况来改善这种情况。

图 2:由 3.3 伏直流逻辑驱动的 Diodes DDTD113ZC - 7 - F 的电路分析

技术小贴士:

典型的微控制器有两个电流规格,包括每个引脚的规格和所有引脚电流的总和。例如,瑞萨电子 Renesas 的 R7FA4M1AB3CFM#AA0,用于最新的 Arduino UNO R4 开发板。大多数端口能够吸收和输出 4 毫安电流,少数引脚能够承受 20 毫安电流,但所有输出引脚的总电流限制为 60 毫安。因此,需要进行仔细的电路分析,以确保不超出产品的限制。

请注意,这里展示的 Diodes 的 DDTD113ZC-7-F 预偏置晶体管因其 R1 电阻值较低而被选用。对于低电流微控制器,具有较高输入电阻的晶体管可能是更好的匹配。

务必逐个案例(逐个负载)进行评估。

预偏置晶体管的速度有多快?

晶体管的开启和关断速度由负载特性、米勒电容和饱和深度等因素决定。以下是一些与本工程简述直接相关的设计考虑因素:

深度饱和的晶体管关断速度会很慢。根据定义,强制 β 偏置会使晶体管深度饱和,以避开线性区域。这是一个重要的考虑因素,因为在载流子从其硅结构中清除之前,晶体管不会关断。

基极电流取决于微控制器的 I/O 电压以及预偏置晶体管的 R1 / R2 比率。饱和深度也取决于负载。例如,当负载接近 26 毫安的限制时,所示电路的速度比轻载 5 毫安时更快。换句话说,要仔细选择预偏置晶体管以匹配负载,避免过度饱和。

与微控制器的直接连接排除了施加负脉冲以提高关断速度的可能性。此外,由于没有暴露的基极连接,无法实现诸如贝克钳位等加速电路。

综合来看,这些设计限制表明预偏置晶体管以中等速度运行。然而,有许多不同的负载和电平转换应用可以从预偏置晶体管中受益。在所有情况下,设计人员都应选择最合适的预偏置晶体管,以使微控制器与负载实现最佳匹配。

技术小贴士:

请记住,传统上匹配过程是通过选择合适的电阻来完成的。现在,设计人员必须选择具有适合手头任务的内部电阻的预偏置晶体管。例如,R1 为 4.7 千欧甚至 10 千欧的晶体管可能更适合您的设计。

最后

预偏置晶体管是一种方便的方法,可以减小 PCB 尺寸并减少设计中使用的元件总数。务必通过选择具有适当内部电阻的预偏置晶体管,使微控制器与负载相匹配。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码