了解CMRR及其与ADC偏移误差的关系

了解共模抑制比(CMRR)的变化如何影响模数转换器(ADC)的性能。

在不同的应用中,如传感器测量系统和通信系统,我们观察到ADC输入端的共模信号不是恒定的。共模电压的变化可能是由于噪声分量引起的,该噪声分量同样耦合到ADC的两个输入端,或者源于正常的电路操作。

在本文中,我们将看到共模电平的变化如何影响ADC的性能。

为什么ADC的共模抑制很重要?

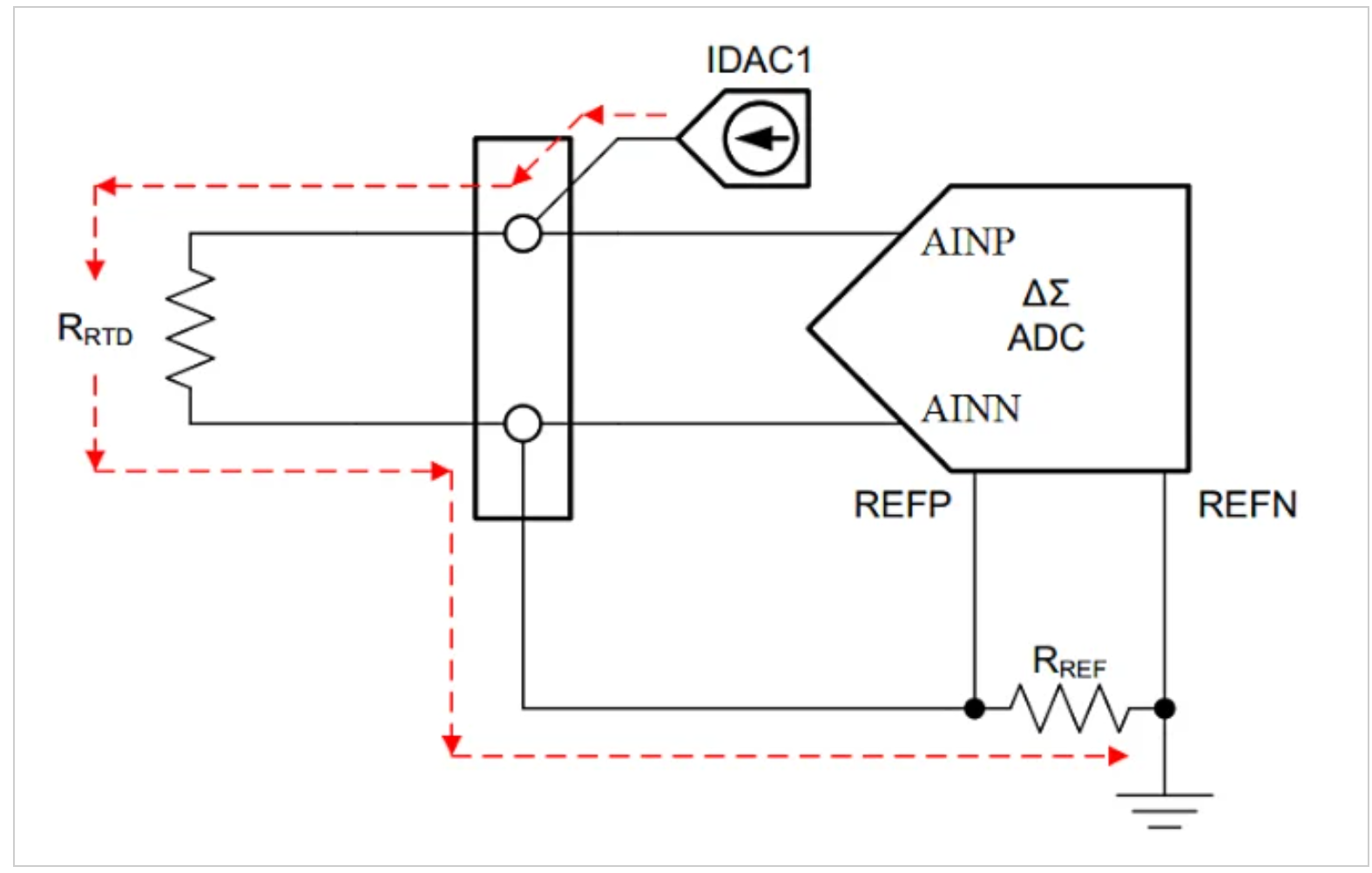

图1显示了RTD测量的简化图。

RTD测量的示例图。

图1. RTD测量的示例图。图片由德州仪器公司提供

在上述示例中,激励电流源迫使固定电流流过RTD和参考电阻器RREF。RTD上的电压由ΔΣ(delta-sigma)ADC直接测量。RREF上的电压也用于提供ADC的参考电压,从而实现比率测量。

除了提供参考电压外,RREF电平将RTD电压移至ADC指定的输入共模范围内。让我们考虑一个100Ω铂RTD系统的一些典型值。假设ADC使用单个3.3V电源工作,激励电流为1mA。通常,中间电源在ADC的共模范围内。基于这个假设,我们可以使用RREF = 1.6 kΩ将RTD信号电平移至1.6 V,这接近电源电压的中点。

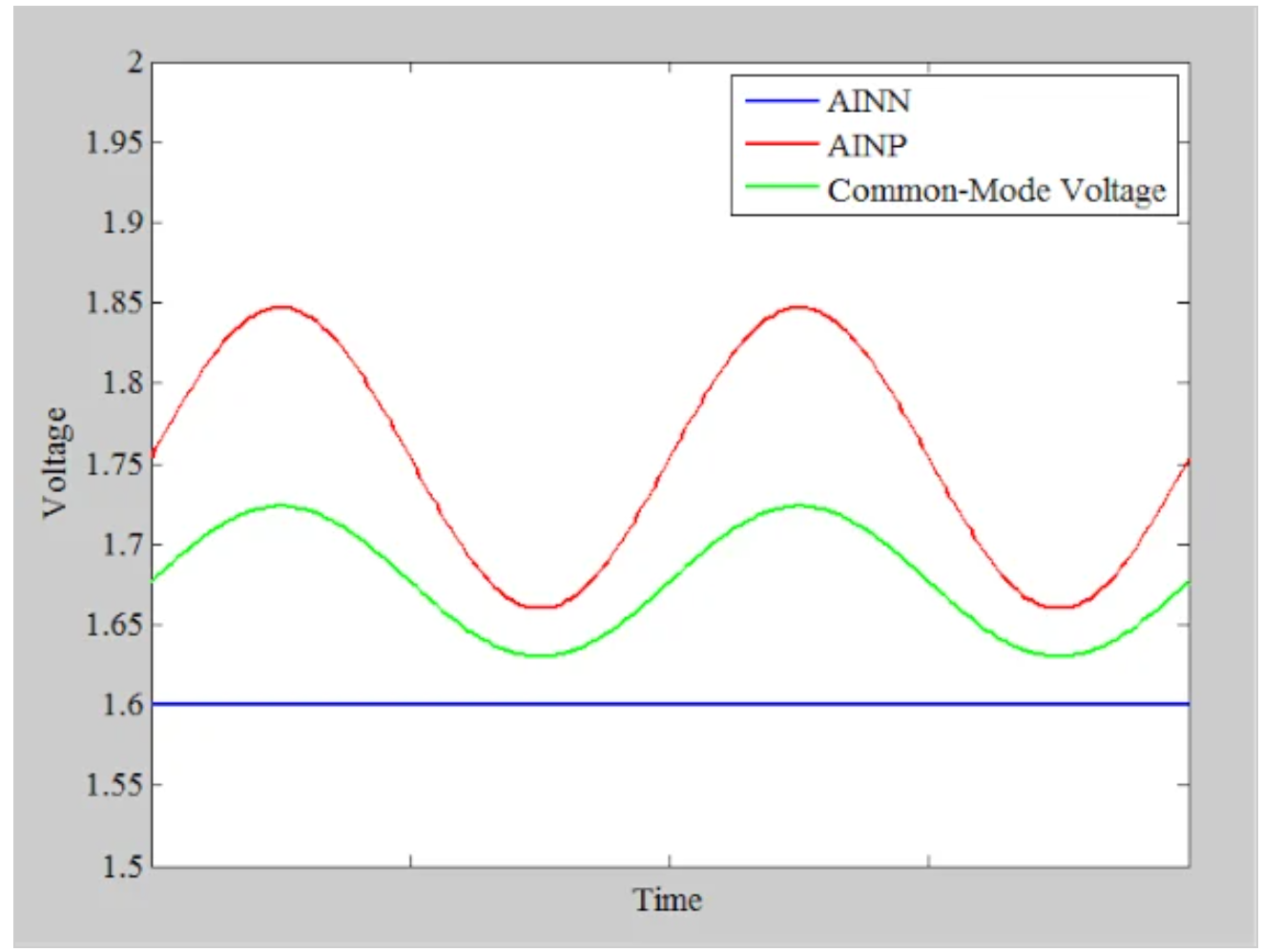

接下来,假设RTD温度从-100°C变化到400°C,RTD电阻从60.256Ω变化到247.092Ω。在这个例子中,AINN输入保持在1.6V,而AINP输入在指定的温度范围内从大约1.66V变化到1.847V。如果我们假设在假设的应用中温度变化遵循正弦波形,则AINN和AINP的电压类似于图2所示的波形。

示例应用图显示了AINN、AINP和共模电压的电压与时间的关系。

图2:示例应用图显示AINN、AINP和共模电压的电压与时间的关系。

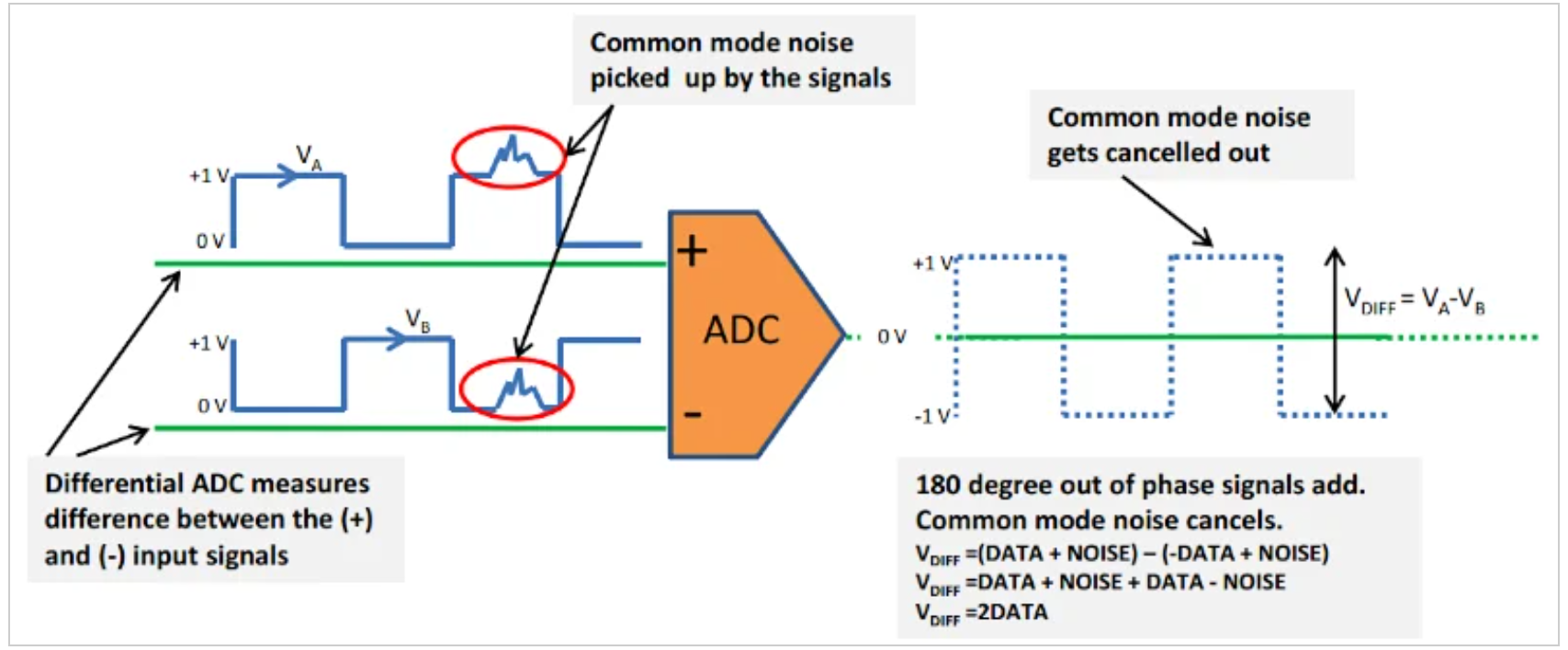

上图中的绿色曲线显示了AINN和AINP的平均值,这是输入端所经历的共模电压。在这个例子中,共模电压不是恒定的,变化了大约100 mVp-p。在理想情况下,这应该不是问题。理想的差分ADC测量其两个输入端之间的电压差,并完全消除任何共模信号,如图3所示。

一个示例ADC测量其两个输入之间的电压差,消除共模信号。

图3. ADC测量其两个输入之间的电压差,消除共模信号的示例。图片由Microchip提供

然而,在现实世界的ADC中,共模信号只是被衰减,而不是被完全抑制。共模抑制比(CMRR)是一个重要的规格,它表征了ADC阻止共模信号出现在ADC输出端的能力。

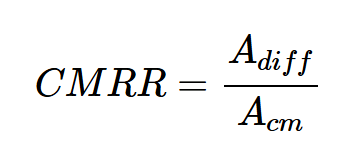

ADC共模抑制比方程

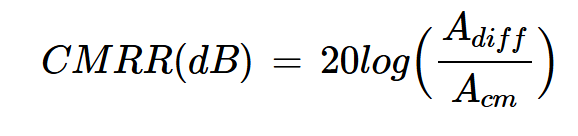

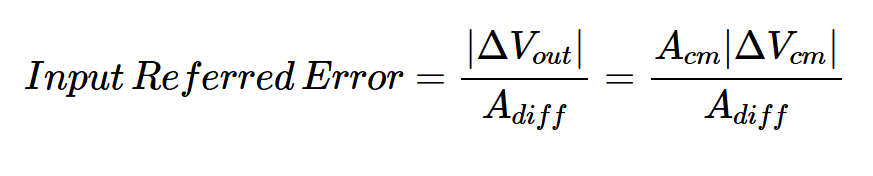

传统教科书中对共模抑制比(CMRR)的定义是电路的差模增益(Adiff)与共模增益(Acm)之比。从数学上讲,我们得到方程式1:

方程式1。

在ADC的上下文中,差模增益是ADC线性模型的斜率,定义为输出码变化与差分输入变化之比。同样,Acm是通过将输出码变化除以输入共模信号变化来求得的。除了输出码变化,我们还可以使用输出码变化的模拟等效值来求得Acm、Adiff和CMRR。CMRR通常使用等式2以dB表示:

方程式2。

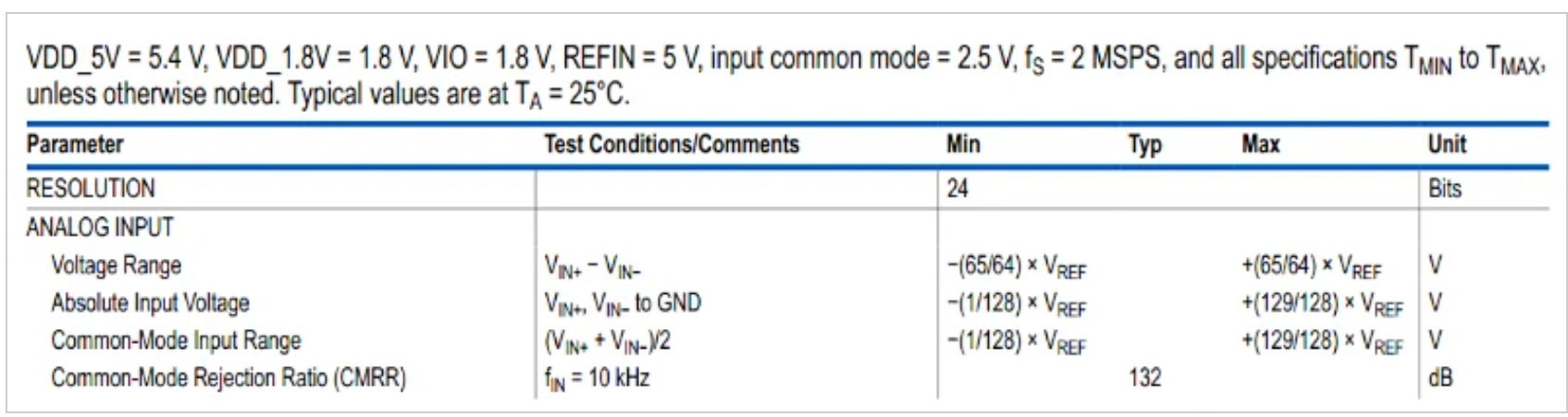

例如,下表提供了AD4030-24的CMRR规格。

表1. 数据由Analog Devices提供

该设备在10 kHz的共模信号下表现出132 dB的CMRR。我们稍后将讨论CMRR规格的一个重要测试条件是输入共模,CMRR是在该条件下测量的。如您所见,AD4030-24 CMRR测试的输入共模为2.5 V。

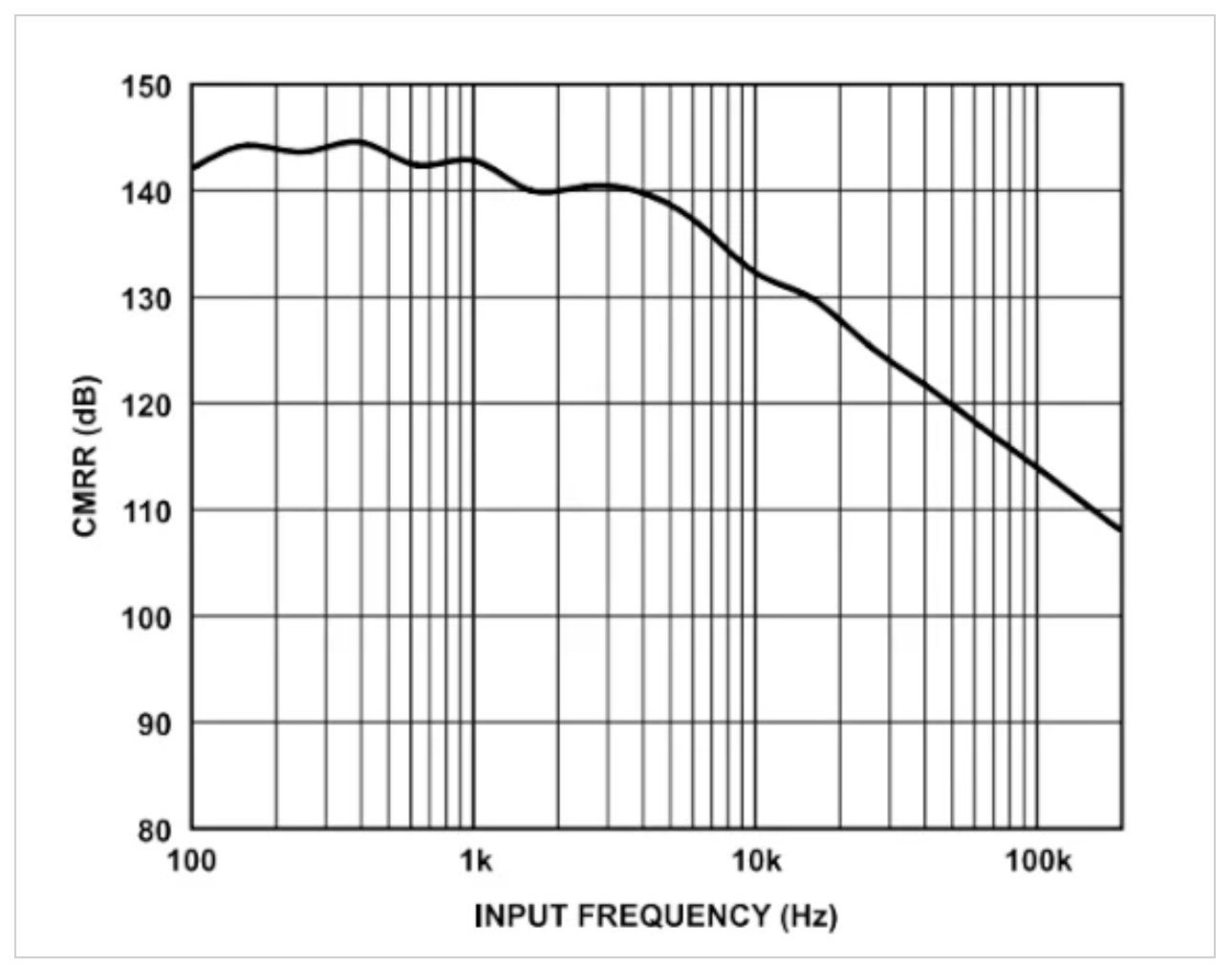

那么,AD4030-24具有132 dB的CMRR意味着什么呢?这意味着,假设Adiff = 1,AD4030-24在输出端将输入共模信号衰减了132 dB。请注意,CMRR规格是频率相关的。数据表通常提供器件CMRR与频率的关系图。图4显示了AD4030-24的CMRR如何随频率变化。

AD4020-24的共模抑制比(CMRR)频率变化。

图4 AD4020-24的共模抑制比(CMRR)频率变化。图片由Analog Devices提供

在10 kHz以下,该设备可以提供大于132 dB的CMRR。如果您考虑特定频率的性能,则应考虑该频率下的CMRR。

共模变化引起的输入错误

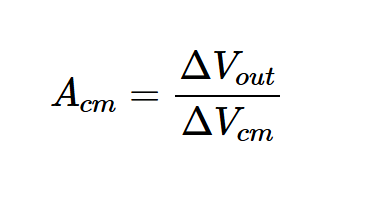

除了上述讨论的方程外,我们还可以通过参考ADC输入的共模变化产生的误差来推导出另一个有用的方程。假设输入共模电压变化ΔVcm,导致输出码变化一定的值。如果输出码变化的模拟等效量为ΔVout,则有:

我们可以说,改变输入共模ΔVcm会在ADC输出端产生不想要的误差ΔVout。为了将此误差与输入相关联,我们可以将其除以ADC差模增益,得到:

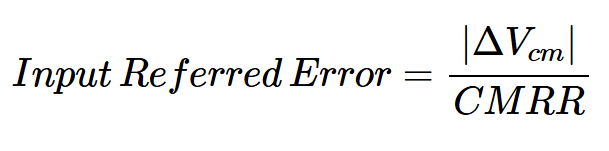

将方程式1代入上述方程式,我们得到方程式3:

方程式3。

这意味着改变共模电压ΔVcm的影响可以通过一个等于的误差项来建模|ΔVcm|CMRR

|ΔVcm|CMRR|ΔVcm|CMRR |ΔVcm|CMRR|ΔVcm|CMRR|ΔVcm|CMRR在ADC输入端。

请注意,我们使用等式1提供的CMRR定义来推导上述等式。如果CMRR以dB为单位给出,则应首先使用等式2找到以V/V为单位的等效CMRR值,然后应用等式3。

让我们来看一个例子。

共模ADC测量示例:

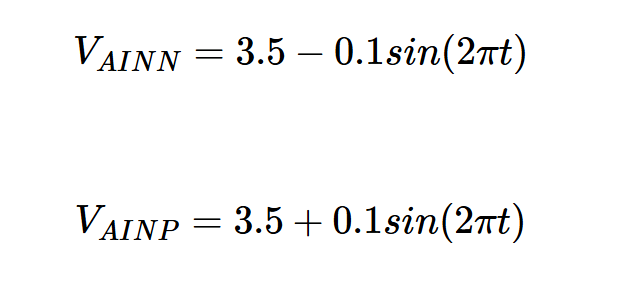

假设在2.5 V的共模输入下测量ADC的不同直流规格,包括CMRR参数。对于低频共模信号,ADC的最小CMRR为100 dB。在我们的应用中,以下信号被应用于ADC差分输入:

如您所见,ADC 在与数据表中指定的测试条件不同的共模电平下使用。这将对性能产生什么影响?

在此示例中,共模输入为3.5 V,而不是数据表测量中使用的2.5 V。通过更改共模输入 |ΔVcm|=1

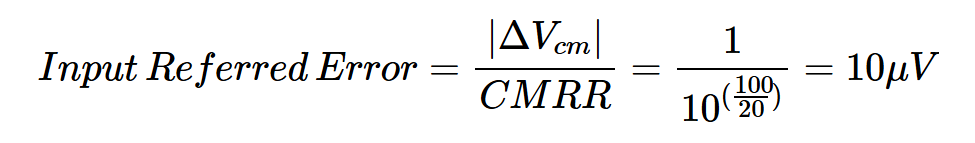

产生一个输入相关的误差项,该误差项可以通过以下方式找到(方程式3):

请注意,100 dB的CMRR会产生

AdiffAcm=105VV,在上述方程式中使用。

这个例子表明,将输入共模电压改变一个固定值会导致恒定的输入参考误差。换句话说,我们可以通过ADC偏移误差的变化来模拟共模值的恒定变化。在上面的例子中,如果数据表偏移误差(在输入共模电压为2.5V时指定)为±30µV,那么我们现在预计它会增加到±40µV。

在ADC输出端,可以很容易地校准出恒定的偏移误差。然而,变化的共模电压会导致ADC输入端出现变化的误差。共模变化可能是由共模噪声引起的,例如来自电力线的50/60 Hz噪声,或者它们可能仅仅源于我们系统的正常运行,就像文章开头讨论的RTD测量系统一样。

关于ADC输入共模范围的一点说明

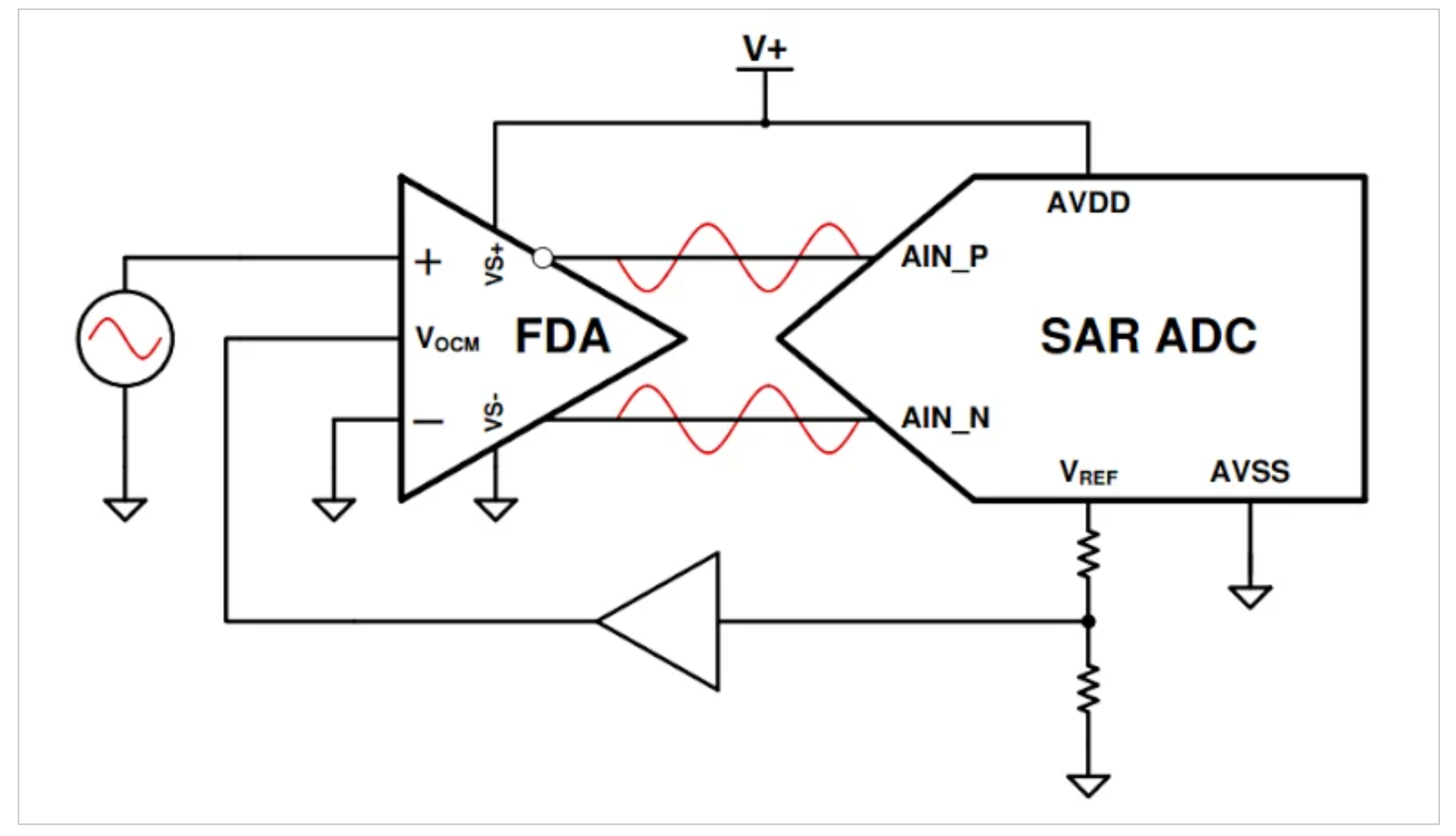

不同的ADC被设计用于支持不同的输入共模范围。许多全差分逐次逼近寄存器(SAR)ADC的输入共模范围仅限于VREF/2附近的小范围。典型范围为(VREF/2)±100 mV。在这些情况下,我们需要将前一级的输出共模保持在ADC的共模范围内。图5显示了如何使用具有输出共模引脚(Vocm)的全差分放大器(FDA)将FDA输出的共模电平固定在VREF/2。

图表显示了一个全差分放大器,带有一个输出共模引脚,用于固定共模电平。

图5. 示意图显示了带有输出共模引脚的全差分放大器,用于固定共模电平。图片由德州仪器(TI)提供

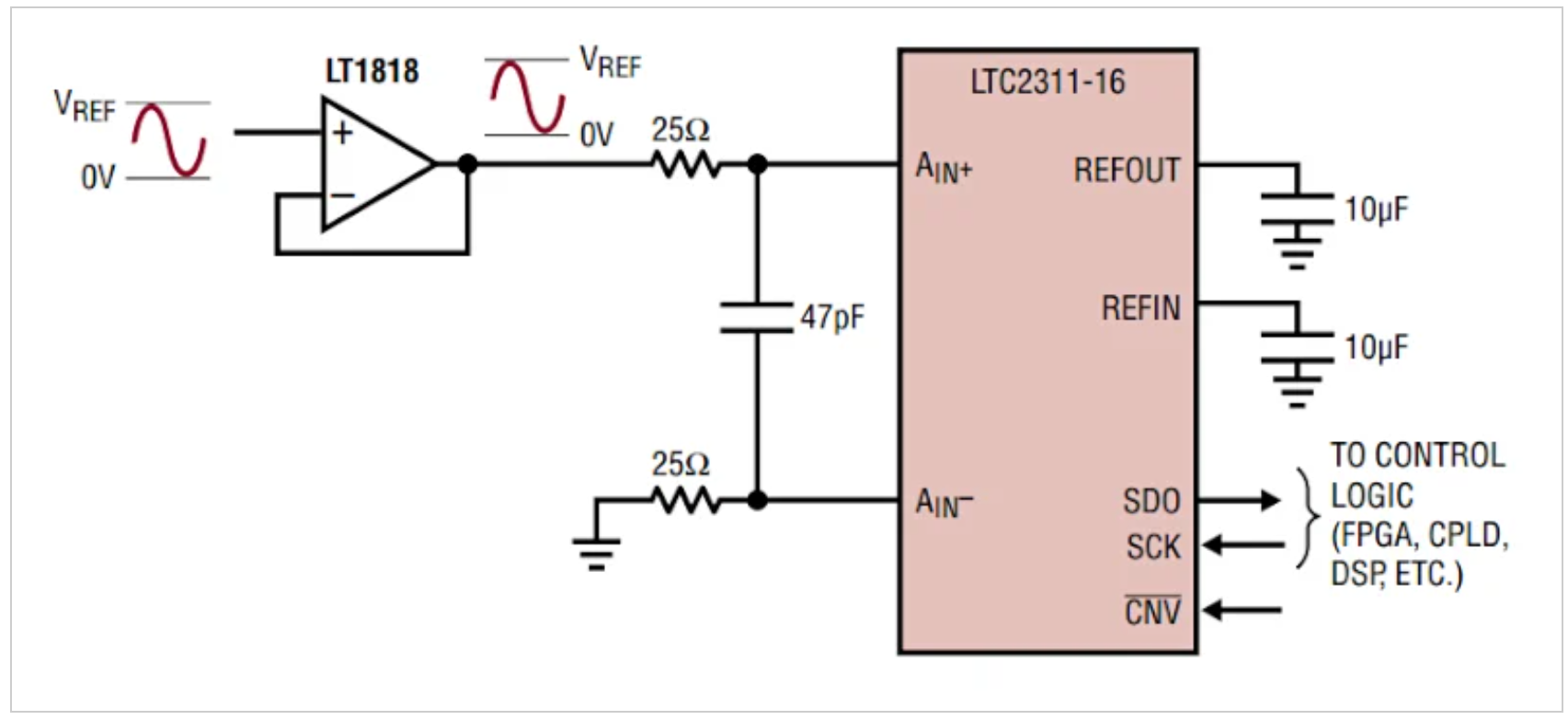

此外,还有输入共模范围较宽的SAR ADC。这种类型的例子(图6)是Analog Devices的LTC2311-16。

LTC2311-16的方框图。

图6 LTC2311-16的框图。图片由Analog Devices提供

该器件的宽输入共模范围允许不同的输入配置,例如如下所示的伪差分单极配置。请注意,在此示例中,输入共模从0变化到VREF/2。

另一方面,大多数ΔΣ ADC的设计目标是提供比SAR ADC相对较大的输入共模范围。由于许多ΔΣ ADC内置了可编程增益放大器(PGA),应注意的是,如果我们配置PGA以更高的增益运行,ADC的共模范围可能会更小。

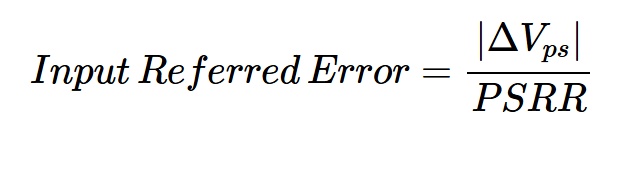

ADC电源抑制比(PSRR)

电源抑制比(PSRR)是ADC抑制电源变化的能力。与CMRR效应类似,有限PSRR的效应可以建模为ADC输入端的误差源。在这种情况下,输入参考误差由下式给出:

解释:

|ΔVps|表示电源电压的变化。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码