共漏极放大器介绍:大信号行为

共漏极放大器也称为源极跟随器,以其低输出阻抗而闻名。本文介绍了基本的公共漏极配置,并研究了其大信号特性。

理想情况下,运算放大器的输出电阻应为零。这是因为运算放大器的输出电阻与负载电阻串联,因此这两个电阻将形成一个分压器。对于非零输出电阻,这将导致负载处的输出电压降低。

尽管它被广泛使用,但共源放大器在这方面远非理想。它的输出阻抗与MOS晶体管的输出电阻在同一数量级,很容易达到几kΩ。因此,用输出阻抗相对较低的另一个放大器缓冲共源放大器的输出是有用的。

进入共漏极放大器。虽然它的使用频率不如其公共源极对应物,但当放置在运算放大器的输出端时,它可以形成一个很好的电压缓冲器:它的小信号增益大约为1,输出电阻相对较小。当创建振荡器或两端有源电感器时,该放大器的输入和输出阻抗也很有用。

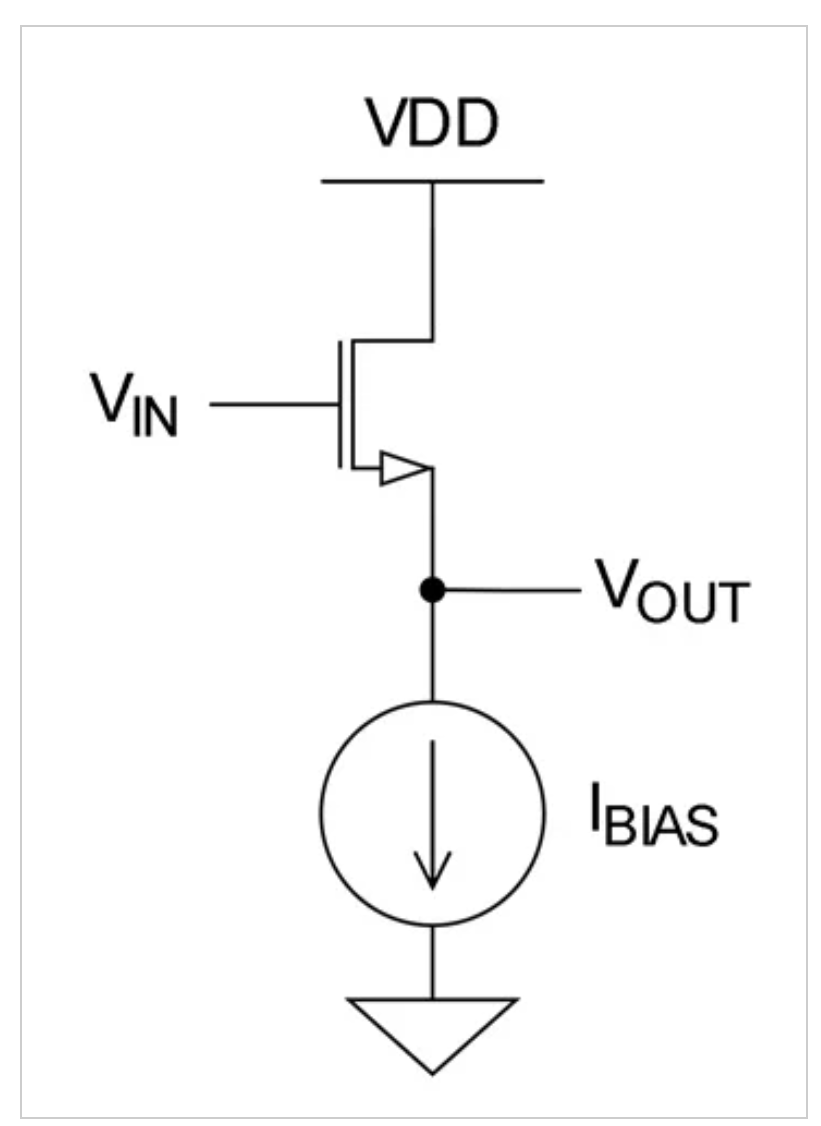

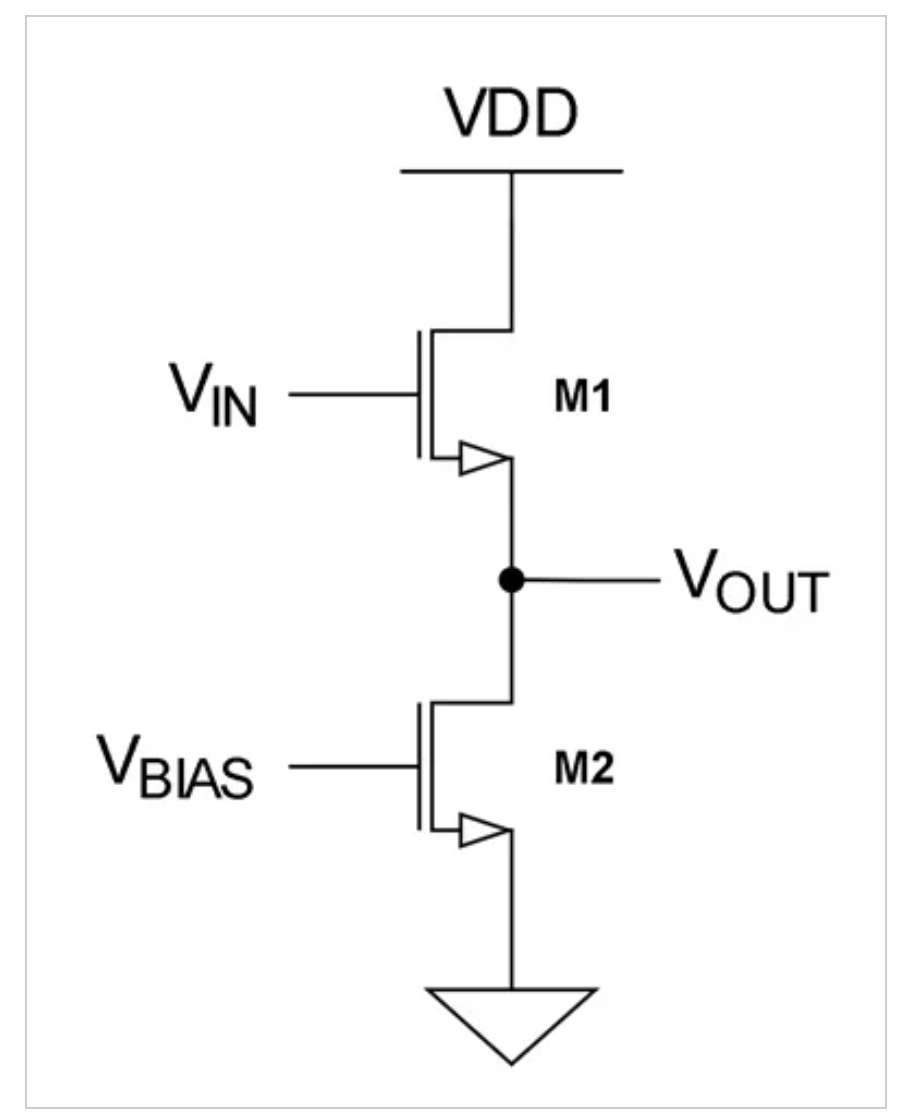

图1显示了具有理想电流源的基本共漏极放大器。

具有理想电流源的基本共漏极放大器。

图1。基本的共漏极放大器配置。

如上图所示,共漏极放大器使用栅极作为输入,源极作为输出。因为源极的输出电压“跟随”栅极的输入电压,所以这种配置也被称为源极跟随器。漏极与直流电压相连。对于NMOS,假设直流电压为VDD;对于PMOS,它是地。

在本文中,我们将了解此源跟随器的大信号特性。后续文章将介绍放大器的小信号行为。

理想电流源的大信号行为

为了理解上述电路的大信号特性,让我们看看当我们将VIN从0扫到VDD时,VOUT会发生什么。

在扫描开始时,VIN和VOUT都等于0。只要VIN小于NMOS晶体管的阈值电压(VTH),晶体管将保持关断,VOUT将继续为0。然而,一旦VIN达到阈值电压,晶体管就会导通。

当它打开时,晶体管处于饱和状态。当VDS=VGS-VTH时,NMOS晶体管达到饱和。由于在这种配置中VDS=VDD,并且VDD将始终大于VGS-VTH,因此晶体管将在剩余的扫描时间内保持饱和。

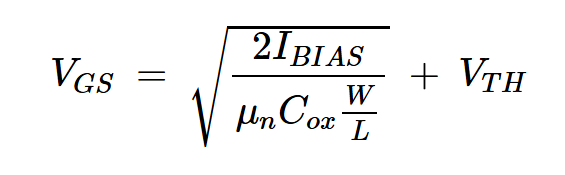

一旦晶体管导通,电流源就会迫使偏置电流(IBIAS)通过晶体管。在此基础上,我们可以计算栅极到源极的电压,如下所示:

方程式1。

解释:

μn是NMOS晶体管的迁移率

Cox是氧化物电容

W是晶体管宽度

L是晶体管长度。

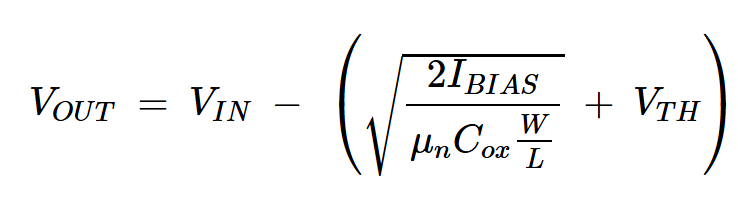

由于在这种情况下VGS等于VIN-VOUT,我们可以重新排列这个方程来求解VOUT:

方程式2。

从方程式2中可以看出,VOUT在较低电压下跟随VIN。这指向了源跟随器的一个常见应用,即它可以用作电平移位器。

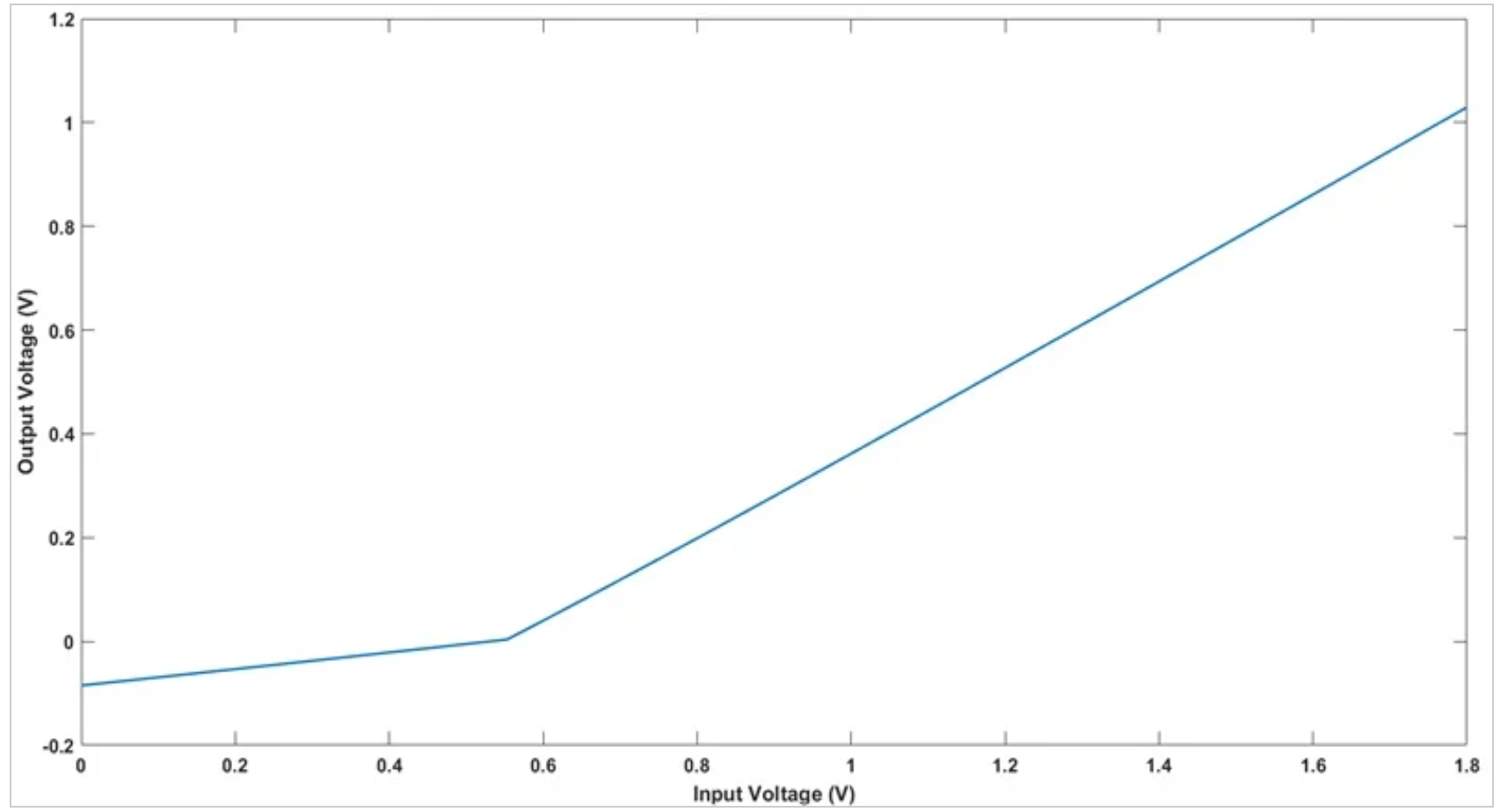

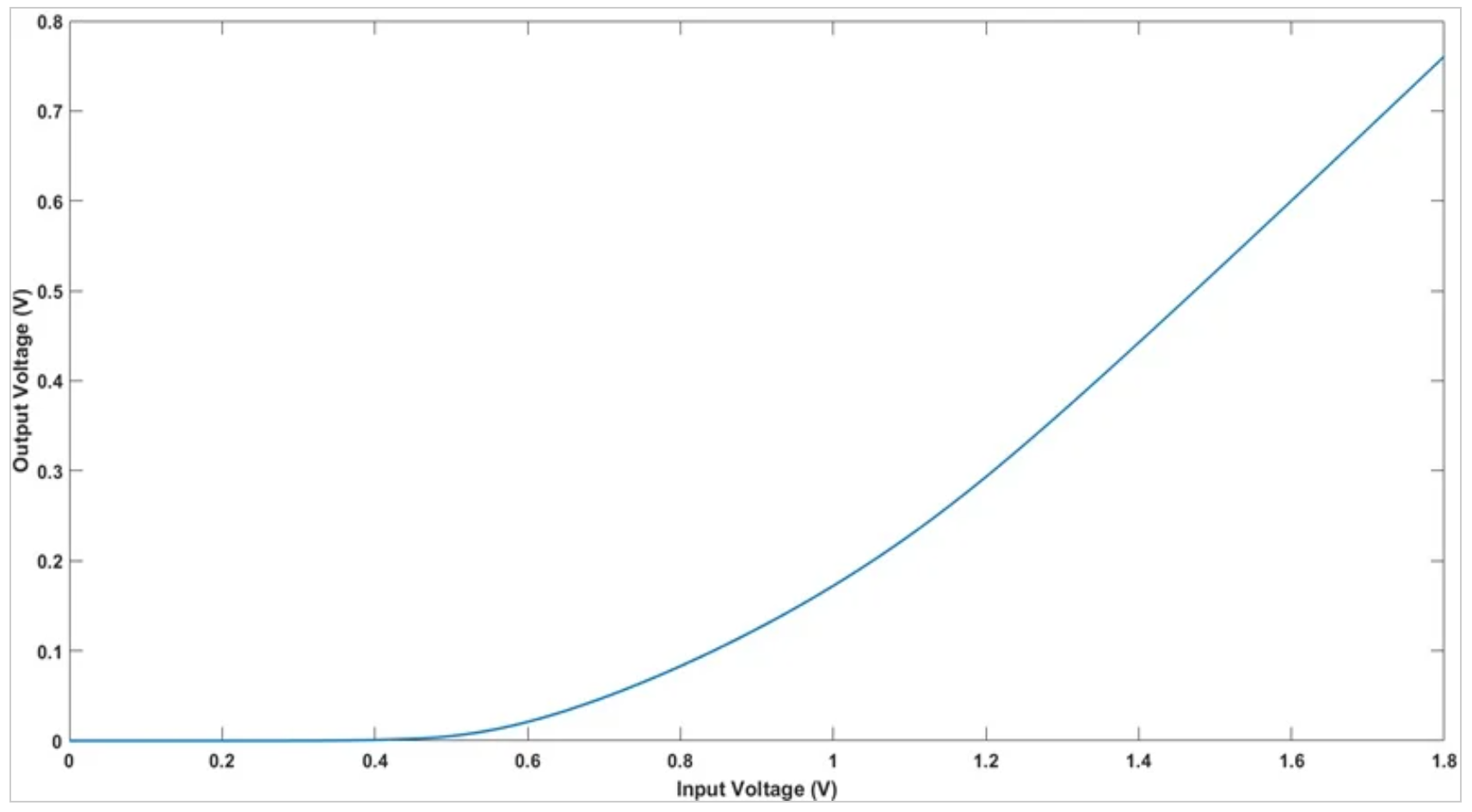

图2展示了图1中共漏极放大器的大信号特性。图表上的输出电压变为负值,因为电路中使用了理想的电流源。

具有理想电流源的共漏极放大器的直流特性。

图2:图1中公共漏极放大器的直流特性。

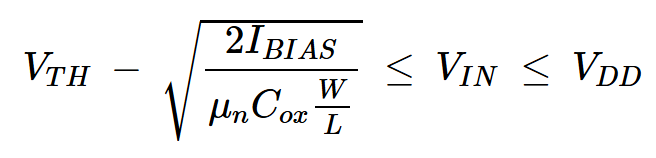

公共漏极放大器输入电压的适当工作区域由下式给出:

方程式3。

更现实的实施

因为它使用了一个理想的电流源,图1并不能代表我们实际如何实现一个共漏极放大器。在现实生活中,电流源将通过负载晶体管实现,如图3所示。负载晶体管标记为M2。

带MOS电流源的共漏极放大器。

图3。带MOS电流源的共漏极放大器(M2)。

M2必须处于饱和状态才能正常工作,因此该放大器的大信号特性略有不同。当VOUT≥VBIAS-VTH时发生饱和。如果VOUT低于VBIAS-VTH,M2将在线性区域运行,从而降低源极跟随器的性能。

图3的直流特性如图4所示。

具有MOS电流源的共漏极放大器的直流特性。

图4。MOS电流源共漏极放大器的直流特性。

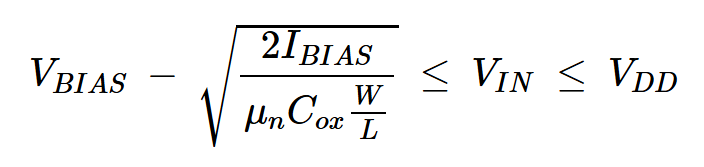

因为VBIAS必须大于VTH,所以我们的工作范围比理想电流源更有限。使用方程式2中VOUT与VIN的关系,我们可以定义此版本的共漏极放大器正常工作的VIN范围:

方程式4。

总结

从我们的大信号分析中,我们可以看到源极跟随器输出输入的电平偏移电压。因为输出跟踪输入的变化,所以公共漏极放大器可以用作缓冲器或电平移位器。在下一篇文章中,我们将研究源代码跟随器的小信号行为,了解它的更多用途。

关键词: 共漏极放大器

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码