修改LTspice中数字组件的操作

定制LTspice逻辑门和触发器的设备参数可以帮助您更准确地模拟这些组件。本文将介绍规范制定过程,并提供一些有用的提示。

本系列的第一篇文章讨论了LTspice逻辑门组件的底层电气结构,特别关注了未使用与逻辑低输入的棘手问题。在本文中,我们将看到调整这些组件的某些设备参数如何使我们能够定制它们的电气行为。我们的重点将放在以下关键参数上:

逻辑电压。

过渡时期。

输出阻抗。

图1显示了一个基本的双输入AND电路的低到高输出转换,其中所有这些参数都处于默认状态。

LTspice中具有默认器件参数的双输入AND门的低到高输出转换。

图1。具有默认参数的LTspice AND门的低到高输出转换。

上图为我们的讨论提供了一个基线。在本文中,我们将研究修改AND门的不同参数如何改变我们的模拟结果。让我们从电路的逻辑电平开始。

逻辑电压

LTspice的数字元件默认电压方案为1V逻辑,阈值电压(Ref)介于逻辑低和逻辑高之间。换句话说,默认值是:

Vlow=0 V

V高=1 V

参考=0.5 V

要更改一个或多个电压参数,请右键单击栅极符号。这将打开组件属性编辑器。然后,将新的电压规格添加到SpiceLine字段中。

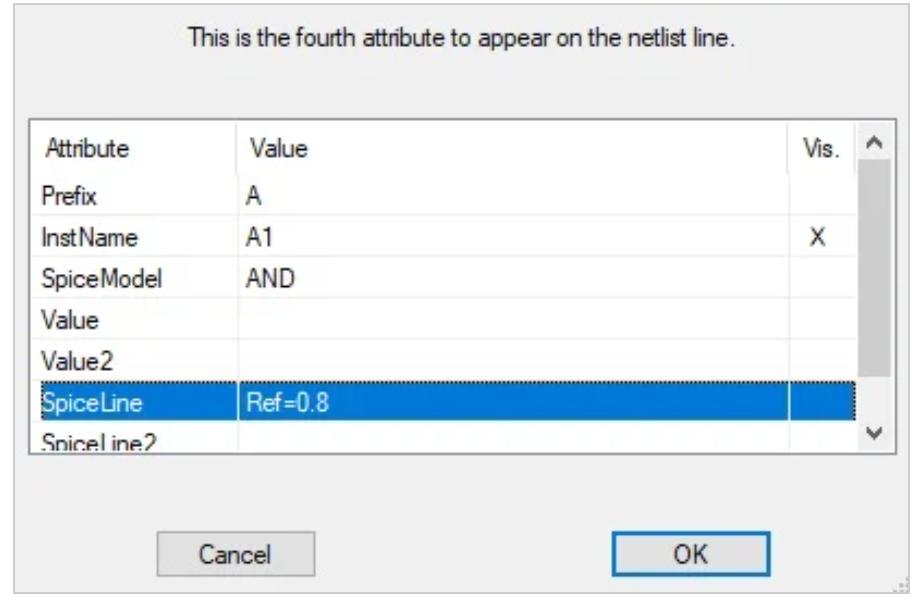

例如,让我们尝试在SpiceLine字段中键入Ref=0.8(图2)。这应该会将阈值电压从默认值(0.5 V)更改为0.8 V。

在LTspice组件属性编辑器中更改AND门的阈值电压。

图2:更改LTspice中的阈值电压。

图3显示了更改后从低到高的输出转换。如光标框所示,阈值电压现在为0.8V。

AND栅极低至高输出转换,阈值电压设置为0.8V。

图3。阈值电压设置为0.8V时,从低到高的输出转换。

因为我们没有为Vhigh或Vlow指定任何值,所以当我们运行上述模拟时,它们仍然是默认值。让我们改变这一点。我们将为该电路提供0.2V的逻辑低电压和2.5V的逻辑高电压。

如图4所示,这些电压以与阈值电压完全相同的方式添加到LTspice中。

调整AND门的逻辑低电压和逻辑高电压。

图4。调整AND门的逻辑低电压和逻辑高电压。

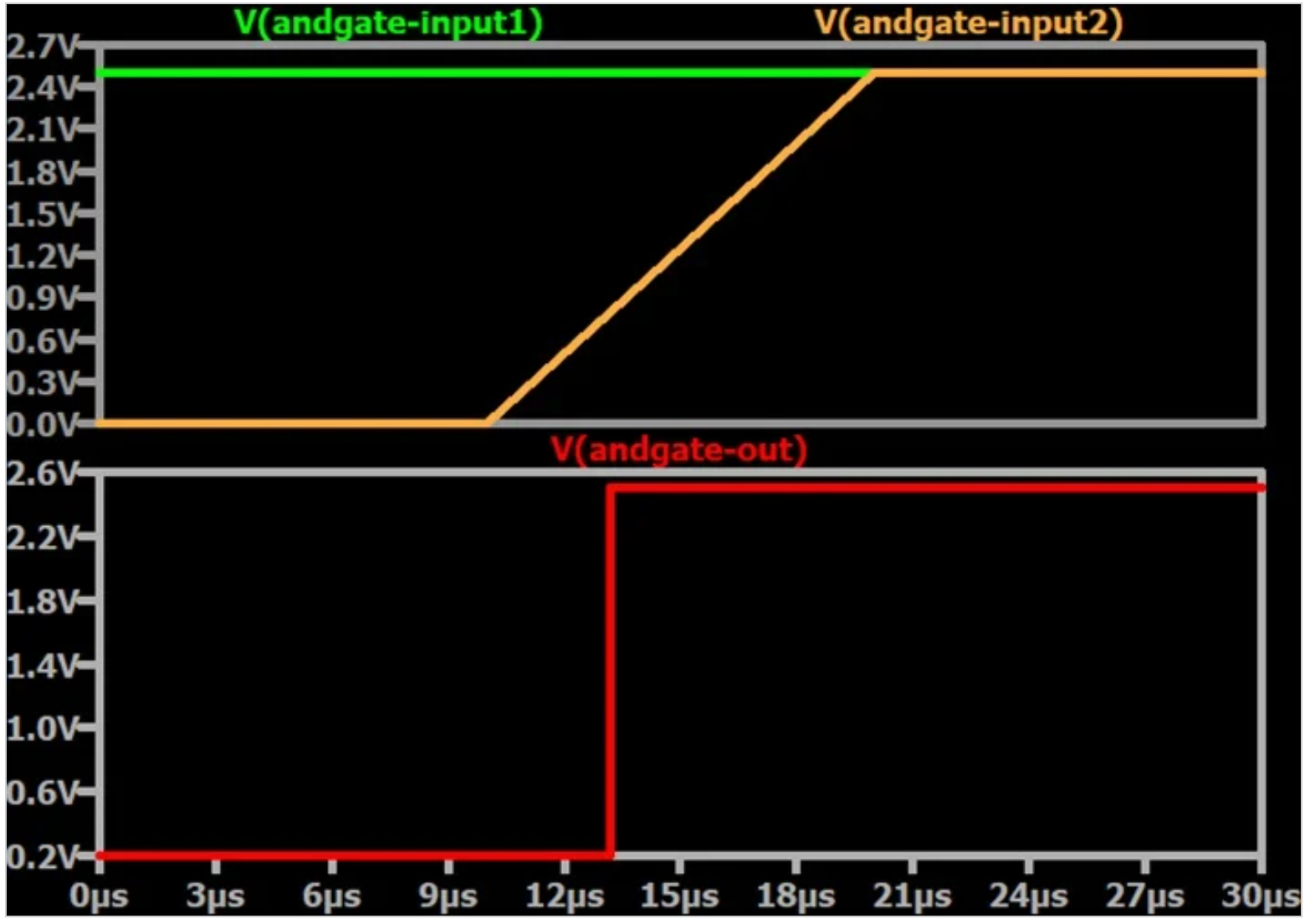

图5显示了使用新的Vhigh、Vlow和Ref值从低到高的输出转换。

LTspice AND门的低到高输出转换,具有为逻辑低、逻辑高和阈值电压指定的自定义值。

图5。在SpiceLine字段中输入了Vhigh=2.5、Vlow=0.2和Ref=0.8的示例AND门的低到高输出转换。

我们现在已经看到了为以下对象指定自定义值时电路的行为:

所有三个电压参数(图5)。

三个电压参数都没有(图1)。

只有阈值电压(图3)。

但是,如果只有逻辑高电压和逻辑低电压而不是阈值电压具有自定义值,会发生什么?

根据LTspice文档,逻辑门的输入阈值默认为(Vlow+Vhigh)/2。如果逻辑低电压和逻辑高电压仍然处于各自的默认值0 V和1 V,那么我们将得到图1中看到的0.5 V阈值电压。然而,对于我们上面选择的Vlow和Vhigh值,删除Ref规范后,我们得到了以下阈值电压:

图6中的模拟结果证实了这一点。

当未指定参考值时,AND门的阈值电压默认为逻辑低电压和逻辑高电压之间的一半。

图6。删除Ref规范后,阈值电压默认为逻辑低电压和逻辑高电压之间的一半。

接下来,让我们考虑电路的转换时间。

过渡时间

默认情况下,LTspice中数字组件的下降时间(Tfall)等于其上升时间(Trise)。如果——通常情况下——你想让上升和下降时间相同,你只需要指定Trise。Trise的默认值为0,因此您可能确实希望至少指定一个上升时间。如果你不这样做,你将有一个零上升时间和零下降时间(Tfall=Trise=0),这将使输出变化的过渡时间短得不切实际。

图7显示了我们在图5中使用的AND门设置的放大输出转换。为逻辑高、逻辑低和阈值电压指定值,但不指定上升或下降时间。

AND门低至高输出转换,默认上升时间。

图7。从低到高AND门转换的默认上升时间。

我之前说过,默认情况下,上升时间为零。然而,图7显示,我们的上升时间为147ns——相当短,但绝对不是零。这是因为它受到模拟时间步长的限制。如果我右键单击模拟命令并将100p插入最大时间步长字段,则上升时间将减少到时间步长值(图8)。

从低到高的输出转换,具有默认的上升时间和100 ps的模拟时间步长。

图8。从低到高的输出转换,默认上升时间和模拟时间步长设置为100 ps。

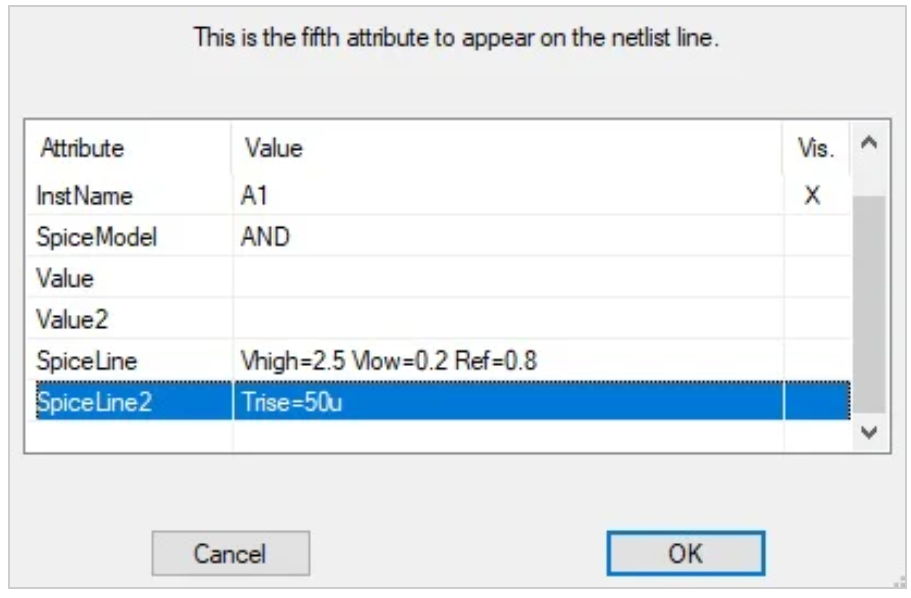

让我们将上升时间设置为50μs。如图9所示,该过程与我们输入电压参数的方式相同。

在LTspice的组件属性编辑器中设置上升时间。

图9。在组件属性编辑器中设置上升时间。

图10显示了新上升时间的低到高输出过渡。

从低到高的AND门转换,具有自定义上升时间。

图10。从低到高的转变,上升时间设置为50μs。

在数字逻辑电路中,上升和下降时间通常被定义为电压完成80%的完全转变所需的时间。然而,LTspice将这些闸门的上升和下降时间定义为过渡的100%。理论上,图10应显示电压上升2.5V。

在实践中,我们可以看到,电压在50μs后仅上升到2.452V,误差为1.9%。这种变化可能是由于LTspice收敛设置造成的,该设置控制模拟器何时决定产生的电压和电流足够接近。更改收敛设置超出了本文的范围。

输出阻抗

默认输出阻抗为1Ω。对于通用数字逻辑来说,这相当低——更现实的选择是10到80Ω之间。当数字输出连接到高阻抗、低电容负载(如典型的数字输入)时,这种差异并不重要。

有时,更高的值可以改善模拟。例如,如果你想为数字设备必须提供或吸收大量电流的电路产生精确的模拟波形,那么1Ω输出阻抗的模拟可能会产生误导。

根据LTspice文档,您可以使用Rout参数指定数字元件的输出阻抗。然而,在我使用AND门和缓冲门进行的实验中,模拟结果与文档中提供的Rout描述不一致。如果你需要增加数字元件的输出阻抗,我建议添加一个外部电阻器,然后检查你的结果以确保它们有意义。

下一篇

在本文中,我们讨论了如何通过定制各种重要参数来改进包括数字组件的模拟。在下一篇文章中,我们将把新知识应用于在LTspice中创建并行负载移位寄存器的任务。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码