imec展示单片式CFET功能组件 成功垂直堆栈金属接点

于本周举行的2024年IEEE国际超大规模集成电路技术研讨会(VLSI Symposium)上,比利时微电子研究中心(imec)首次展示了具备电性功能的CMOS互补式场效晶体管(CFET)组件,该组件包含采用垂直堆栈技术形成的底层与顶层源极/汲极金属接点(contact)。虽然此次研究的成果都在晶圆正面进行接点图形化,不过imec也展示了改从晶圆背面处理接点图形的可行性—这能大幅提升顶层组件的存活率,将其从11%提升到79%。

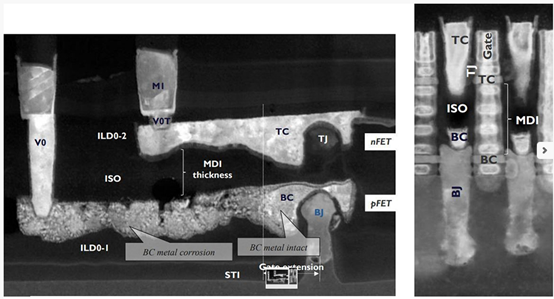

CMOS互补式场效晶体管(CFET)组件搭配中间介电层(MDI)以及从晶圆正面进行图形化的堆栈接点(TC为顶层金属接点,TJ为顶层异质接面,BC为底层金属接点,BJ为底层异质接面)。

imec所规划的逻辑技术蓝图预计将在7埃米(A7)的技术节点引进CFET组件结构。利用辅助的先进布线技术,CFET可望把标准单元的轨道高度从5轨降到4轨,甚至更低,同时确保组件的性能无损。在用来垂直堆栈nMOS与pMOS组件的不同做法中,单片式整合与现有的奈米片制程相较,属于最不具破坏性的技术。

在2024年IEEE国际超大规模集成电路技术研讨会上,imec首次展示具备底/顶两层堆栈接点的单片式CFET功能组件。这些CFET组件以18奈米的闸极宽度进行整合,闸极间距为60奈米,n型与p型组件的垂直距离为50奈米。测试组件验证了这款组件的电气性能,该测试组件包含共享一个闸极的n型与p型场效晶体管,以及从晶圆正面进行连接的顶层与底层金属接点。

imec所提出的这套制程包含两个CFET专用模块:中间介电隔离层(middle-dielectric isolation,以下简称为MDI)、底层与顶层堆栈接点。

中间介电层(MDI)是imec领先开创的制程模块,用来隔离顶层及底层闸极,并区分n型与p型组件的临界电压值。MDI模块的设计基础是针对CFET组件的「主动式」硅/硅锗(SiGe)多层堆栈进行调整;这套模块可以实现内衬层的共整合—内衬层是奈米片结构的特有特色,用来隔绝闸极与源极/汲极。

比利时微电子研究中心(imec)CMOS组件技术计划主持人Naoto Horiguchi表示:「我们采用了中间介电层优先(MDI-first)的做法,在制程控制方面取得最佳成果,也就是在进行源极/汲极蚀刻之前,在奈米片与中间介电层(MDI)之间『劈开』通往通道侧壁的空间,然后进行源极/汲极的磊晶成长。运用一种搭配『原位覆盖技术(in-situ capping)』的创新方法,在蚀刻源极/汲极时就能保护闸极硬光罩/闸极隙壁,实现中间介电层优先(MDI-first)制程。」

第二个关键模块是以垂直堆栈的方式来制出组件底层及顶层的源极/汲极接点,并在垂直方向实现介电隔离。主要的步骤包含:底层接点在填充金属之后重新蚀刻,接着填充介电材料,然后再次蚀刻,与处理MDI堆栈的状况相同,这些过程都是在相同尺寸的有限空间下进行。

Naoto Horiguchi表示:「在研究从晶圆正面来连接组件底层接点时,我们面临了许多挑战,这些挑战影响了底层接点的电阻,还限制了顶层源极/汲极组件制造的制程操作容许范围(process window)。在2024年VLSI会议上,我们展示了把底层接点制程转移到晶圆背面进行的可行性,尽管这会需要多做几个步骤来处理晶圆接合及薄化,但是顶层组件的存活率从11%攀升到79%,这能吸引业界考虑从晶背处理底层接点的制程方案。目前的研究还在努力找出最佳的接点布线技术。」

关键词: imec 单片式 CFET 功能组件 垂直堆栈金属接点

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码