混合键合在3D芯片中发挥着重要作用

上周,IEEE电子元件与技术会议(ECTC)的研究人员推动了一项对尖端处理器和存储器至关重要的技术。该技术被称为混合键合,将两个或多个芯片堆叠在同一封装中,使芯片制造商能够增加其处理器和存储器中的晶体管数量,尽管曾经定义摩尔定律的传统晶体管收缩速度普遍放缓。来自主要芯片制造商和大学的研究小组展示了各种艰苦奋斗的改进,包括应用材料公司、Imec、英特尔和索尼在内的一些研究小组显示的结果可能导致3D堆叠芯片之间的连接密度达到创纪录的密度,即在一平方毫米的硅中约有700万个链接。

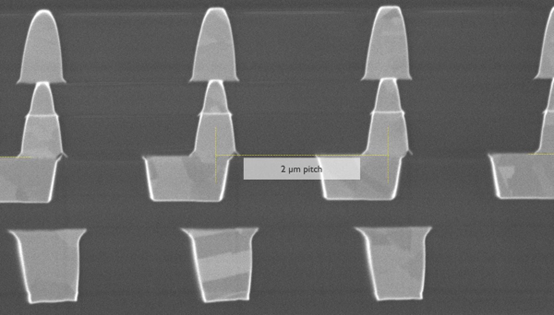

Imec设法在每2微米放置一次的芯片之间建立3D连接。

由于半导体进步的新性质,所有这些连接都是必需的,英特尔的Yi Shi告诉ECTC的工程师。正如英特尔技术开发总经理 Ann Kelleher 在 2022 年向 IEEE Spectrum 解释的那样,摩尔定律现在由一个称为系统技术协同优化 (STCO) 的概念支配。在STCO中,芯片的功能,如缓存、输入/输出和逻辑,被分离出来,并使用最好的制造技术来制造。然后,混合键合和其他先进的封装技术可以重新组装它们,使它们像一块硅一样工作。但这只能通过高密度的连接来实现,这种连接可以在硅片之间穿梭位,几乎没有延迟或能耗。

混合粘接不是唯一使用的先进封装技术,但它提供了最高密度的垂直连接。根据Besi技术高级副总裁Chris Scanlan的说法,它主导了ECTC,约占所提出研究的五分之一,他的工具是几项突破的幕后推手。

“很难说极限是什么。事情进展得非常快。—JEAN-CHARLES SOURIAU,CEA LETI

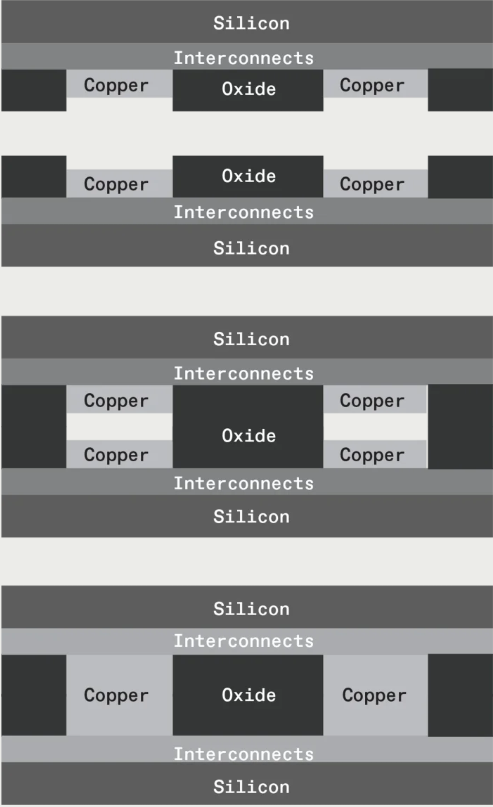

在混合键合中,铜焊盘构造在每个芯片的顶面。铜被绝缘层包围,通常是氧化硅,焊盘本身从绝缘层表面略微凹陷。氧化物经过化学改性后,将两个芯片面对面压在一起,使凹陷的焊盘与每个芯片对齐。然后慢慢加热这个三明治,使铜在间隙中膨胀,连接两个芯片。

混合键合可以将一种尺寸的单个芯片连接到装满更大尺寸芯片的晶圆上,也可以用于将两个相同尺寸的完整晶圆粘合在一起。在一定程度上,由于它在相机芯片中的使用,后者比前者更成熟。例如,Imec报道了一些有史以来最密集的晶圆对晶圆(WoW)键,键与键之间的距离(或间距)仅为400纳米。同一研究中心为晶圆芯片 (CoW) 场景管理了 2 微米间距。(如今的商用芯片的连接间隔约为 9 μm。

混合键合首先在芯片顶部形成凹陷的铜焊盘。当两个芯片压在一起时,周围的氧化物介电键[中间]。退火使铜膨胀以形成导电连接[底部]。

“有了可用的设备,将晶圆与晶圆对齐比将芯片与晶圆对齐更容易。大多数微电子工艺都是为[全]晶圆制造的,“法国研究机构CEA Leti集成和封装科学负责人Jean-Charles Souriau说。然而,晶圆上的芯片(或晶圆到晶圆)在AMD的Epyc系列等高端处理器中引起了轰动,该技术用于在其先进的CPU和AI加速器中组装计算内核和缓存。

在推动这两种情况越来越紧密的间距时,研究人员专注于使表面略微平坦,使结合晶圆更好地粘在一起,并减少整个过程的时间和复杂性。做对了可能最终意味着在芯片设计方式上实现一场革命。

魔兽世界,这些都是一些紧张的音调

晶圆对晶圆 (WoW) 研究报告了最紧密的间距(500 nm 到 360 nm),所有这些都在一件事上花费了大量精力:平坦度。为了以 100 纳米级的精度将两个晶圆绑合在一起,整个晶圆必须几乎完全平坦。如果它弯曲或翘曲,材料的整个部分将无法连接。

展平晶圆是称为化学机械平坦化(CMP)的过程的工作。一般来说,这是芯片制造的关键,特别是对于在晶体管上方产生互连层的工艺部分。

“CMP 是我们必须控制的混合键合的关键参数,”Souriau 说。本周在ECTC上公布的结果将CMP提升到了另一个层次,不仅在晶圆上变平,而且在铜焊盘之间的绝缘层上减少了纳米的圆度,以确保更好的连接。

其他研究的重点是通过试验不同的表面材料(如碳氮化硅而不是氧化硅)或使用不同的方案来化学活化表面,确保这些扁平的部件足够牢固地粘在一起。最初,当晶圆或芯片被压在一起时,它们以相对较弱的氢键固定到位,并且关注的是确保键合和后续步骤之间的一切都保持在原位。然后缓慢加热结合的晶圆和芯片(称为退火的过程)以形成更强的化学键。这些纽带有多牢固,以及如何弄清楚这一点,是ECTC大量研究的主题。

最终的粘结强度的一部分也将来自铜连接。退火步骤使铜在间隙上膨胀,形成导电桥。控制差距的大小是关键,三星的Seung Ho Hahn解释说。间隙太大,铜将无法连接。太少,它会将晶圆推开。这是一个纳米的问题,哈恩报告了对一种新的化学过程的研究,该过程希望通过一次蚀刻一个原子层来使其恰到好处。

连接的质量也很重要。即使在铜膨胀之后,大多数方案表明金属的晶界不会从一侧交叉到另一侧。这种交叉会降低连接的电阻,并应提高其可靠性。日本东北大学的研究人员报告了一种新的冶金方案,该方案最终可以产生跨越边界的大块单粒铜。“这是一个巨大的变化,”东北大学(Tohoku University)副教授福岛孝文(Takafumi Fukushima)说。“我们现在正在分析其背后的原因。

“我认为使用这项技术可以制作 20 层以上的堆栈。”—HYEONMIN LEE,三星

其他实验的重点是简化混合键合过程。一些公司试图降低形成键所需的退火温度(通常在300°C左右),其动机是有可能降低因长时间加热而损坏芯片的任何风险。应用材料公司的研究人员展示了一种从根本上减少退火所需时间的方法的进展——从几小时缩短到仅 5 分钟。

在该领域表现出色的玩家

晶圆上的芯片(CoW)混合键合目前对行业更有用:它允许芯片制造商将不同尺寸的小芯片堆叠在一起,并在每个芯片绑定到另一个芯片之前对其进行测试,确保他们不会用一个有缺陷的部件致命地注定昂贵的CPU。

但 CoW 带来了 WoW 的所有困难,而缓解这些困难的选择更少。例如,CMP旨在压平晶圆,而不是单个芯片。一旦芯片从源晶圆上切割下来并经过测试,就很难提高它们的粘合准备程度。

尽管如此,英特尔报告了间距为 3 μm 的 CoW 混合键合,而 Imec 管理了 2 μm,主要是通过使转移的芯片非常平坦,同时它们仍然附着在晶圆上,并保持它们更加清洁。两个小组的努力都使用等离子蚀刻来切割模具,而不是使用专用刀片的通常方法。等离子体不会导致边缘碎裂,从而产生干扰连接的碎屑。它还允许Imec小组对模具进行成型,制造倒角,以减轻可能破坏连接的机械应力。

几位研究人员告诉IEEE Spectrum,CoW混合键合对于高带宽存储器(HBM)的未来至关重要。HBM 是控制逻辑芯片顶部的一堆 DRAM 芯片,目前有 8 到 12 个芯片高。HBM 通常与高端 GPU 放在同一个软件包中,对于提供运行 ChatGPT 等大型语言模型所需的海啸数据至关重要。今天,HBM 模具使用所谓的微凸块技术进行堆叠,其中每层之间的微小焊料球被有机填料包围。

但随着人工智能进一步推动内存需求,DRAM 制造商希望在 HBM 芯片中实现 20 层或更多层。然而,微凸起占用的体积意味着这些堆栈很快就会太高,无法放入带有 GPU 的封装中。混合键合不仅会缩小HBM的高度,还应该更容易从封装中去除多余的热量,因为其层之间的热阻较小。

200纳米的魔兽世界间距不仅是可能的,而且是可取的。

在 ECTC 上,三星工程师展示了混合键合方案可以制造 16 层 HBM 堆栈。“我认为使用这项技术可以制造20层以上的堆栈,”三星高级工程师Hyeonmin Lee说。

其他新的 CoW 技术可以帮助将混合绑定引入高带宽内存。Souriau说,虽然他们没有在ECTC上展示这方面的研究,但CEA Leti的研究人员正在研究所谓的自对准技术。这将有助于确保使用化学工艺的 CoW 连接。每个表面的某些部分将变得疏水,一些部分将变得亲水,从而使表面自动滑入到位。

在ECTC上,东北大学和雅马哈机器人公司的研究人员报告了类似方案的工作,利用水的表面张力将实验DRAM芯片上的5μm焊盘对齐,精度优于50纳米。

混合键合能走多远?

几乎可以肯定的是,研究人员将继续推动混合键合连接的推销。200纳米的WoW间距不仅是可能的,而且是可取的,台积电(Taiwan Semiconductor Manufacturing Co.)探路系统项目经理Han-Jong Chia告诉ECTC的工程师。台积电计划在两年内推出一种称为背面供电的技术。(英特尔计划在今年年底推出。这项技术将芯片笨重的供电互连置于硅之下,而不是硅之上。台积电研究人员计算,有了这些,最上面的互连层可以更好地连接到较小的混合键合焊盘。使用 200 nm 焊盘的背面供电将大大降低 3D 连接的电容,从而使能效和信号延迟的乘积是 400 nm 焊盘的 9 倍。

Chia建议,在未来的某个时候,如果键距进一步缩小,那么“折叠”电路块可能会变得切实可行,以便将它们构建在两个晶圆上。这样一来,垂直路径可能会使模块内一些较长的连接变得更短,从而可能加快计算速度并降低功耗。

而混合键合可能不仅限于硅。“今天,硅-硅晶圆有很多发展,但我们也在寻求氮化镓与硅晶圆和玻璃晶圆之间的混合键合......一切,“CEA Leti 的 Souriau 说。他的组织甚至提出了关于量子计算芯片混合键合的研究,该研究涉及对准和结合超导铌而不是铜。

“很难说极限是什么,”Souriau说。“事情进展得非常快。”

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码