涨知识!氮化镓(GaN)器件结构与制造工艺

氮化镓功率器件与硅基功率器件的特性不同本质是外延结构的不同,本文通过深入对比氮化镓HEMT与硅基MOS管的外延结构,再对增强型和耗尽型的氮化镓HEMT结构进行对比,总结结构不同决定的部分特性。此外,对氮化镓功率器件的外延工艺以及功率器件的工艺进行描述,加深对氮化镓功率器件的工艺技术理解。在理解氮化镓功率器件结构和工艺的基础上,对不同半导体材料的特性、不同衬底材料的氮化镓HEMT进行对比说明。

一、器件结构与制造工艺

(一)器件结构对比

GaN HEMT是基于AlGaN/GaN异质结,目前市面上还未出现GaN的MOSFET,主要是因为同质GaN成本太高,一般采用Si或者SiC作为异质衬底,异质衬底就需要在衬底上生长一层缓冲层(AlN),而缓冲层是绝缘的,因此目前的GaN器件还没有MOSFET结构。

1、氮化镓HEMT与硅LDMOS的结构对比

图 1 GaN HEMT(增强型) VS 硅LDMOS结构

从结构看,氮化镓功率器件和硅LDMOS都是横向结构,即他们的源极(Source)、栅极(Gate)和漏极(Drain)都在芯片的上表面。同时为了让电场分布更加均匀,他们都使用了场板的设计。不同之处在于氮化镓是化合物半导体外延,通过异质结形成高电子迁移率的二维电子气沟道(2DEG)。而硅LDMOS是在硅外延层上进行掺杂形成P-N结。

2、氮化镓功率器件的结构

氮化镓功率器件的外延结构可分为D-mode(Depletion-mode/耗尽型)和E-mode(Enhance-mode/增强型)。因为材料的极化特性,耗尽型是GaN功率器件的自然状态,增强型只能通过特殊工艺将其阈值电压从负值变成正值来实现。

图 2 E-Mode(增强型) GaN HEMT VS D-Mode(耗尽型) GaN HEMT

目前主要用来制备增强型器件的方案包括:p型栅、凹槽栅、F处理。如上图所示,P-GaN栅结构是实现增强型GaN HEMT的方案之一。本质是通过降低栅下2DEG的电子密度等,实现对栅压的控制,将阈值电压提高到正。

(1)D-mode/耗尽型结构

D-mode为常开型器件,在通常状态下(栅源极电压VGS=0),漏极和源极之间已存在2DEG,器件呈导通状态;当栅源极电压VGS<0时,漏、源极之间的2DEG断开,器件截止。在电力电子应用中,常开的器件在使用上不便且有安全方面的问题,因此D-mode氮化镓HEMT器件在应用中,经常级联/串联低压硅MOS一起使用,如下图所示。

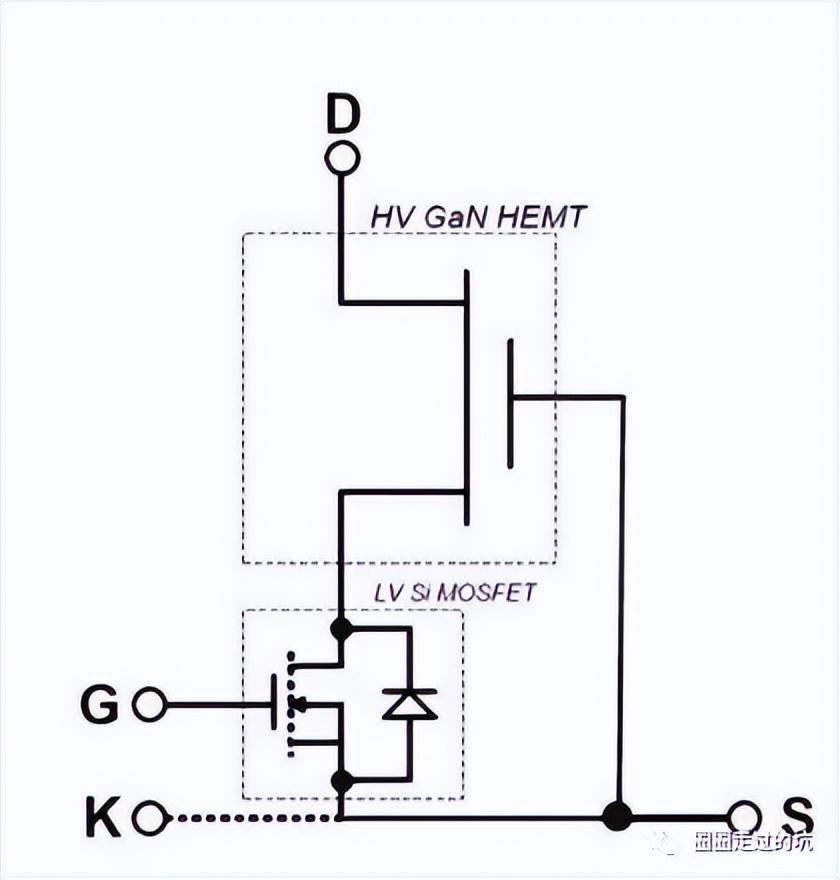

图 3 共源共栅GaN HEMT

D-mode氮化镓功率器件和低压MOSFET串联,共用栅极和源极,形成常关器件。

(2)E-mode/增强型

E-mode(Enhance-mode/增强型)为常关型,使用方式类似传统硅MOS,器件结构简单,适合高频化应用,增强型器件不需要负电压供电,实际应用中的氮化镓功率器件都需要是常关型的器件。

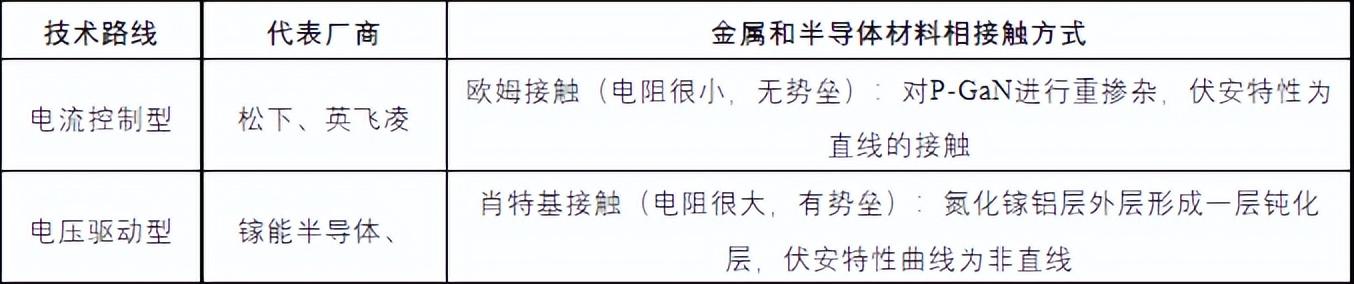

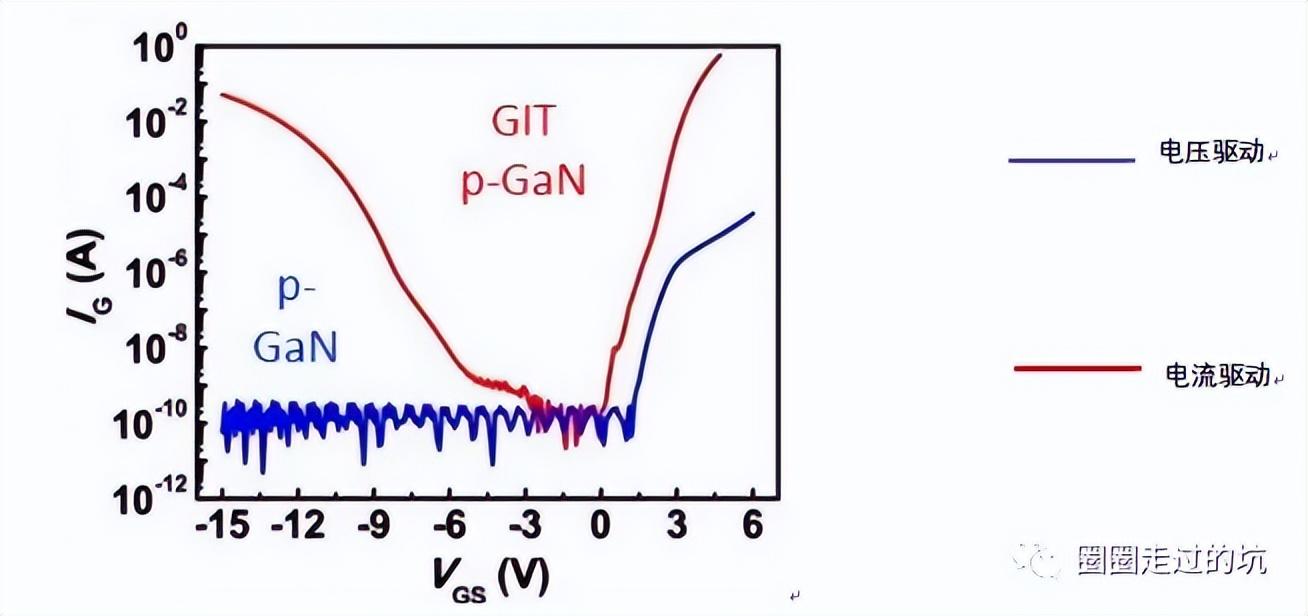

目前主流的增强型器件使用的P-GaN的工艺结构,这种工艺结构带来两类技术路线,对应两种商业模式。一类是以松下和英飞凌为代表的电流控制型。所谓电流控制,指的是门级驱动使用电流,而不是电压来控制。另外一类则是和硅MOS管以及碳化硅MOS管一样,使用门级电压驱动。

表 1 主流增强型P-GaN工艺结构的两种技术路线

图 4 电压驱动 VS 电流驱动曲线

3、基本特性总结

因为结构的不同,氮化镓功率器件和硅基功率器件有区别于硅基器件的特性。

(1)氮化镓功率器件标准:650V

氮化镓功率器件的技术路线一般是650V,因为对于很多电源领域的应用,需要接入220V市电,母线电容上的电压在输入交流电压整流以后得到大约400V直流电压,再加上电压尖峰和部分拓扑结构应用中副边反射回来的电压,650V就成了一个标准的电压要求。

(2)没有雪崩击穿

没有雪崩击穿,一旦击穿,就是永久性的,类似于电容里面的介质击穿。对于650V的器件而言,如果是硅MOS管,一般实际击穿电压大约在750V左右(设计裕量10%),而氮化镓器件需要提供更高的电压设计裕量,650V器件至少需要900V以上的击穿电压(设计裕量>10%)。

(3)没有p型氮化镓管

硅基有NMOS(电子载流子)和PMOS(空穴载流子),但目前还没有p型GaN HEMT,因此模拟/数字IC的设计与硅不同。没有p型氮化镓管的原因主要是:首先,离子注入和镁离子低温退火在GaN上难以实现;其次,GaN的空穴迁移率只有30cm2/Vs,远低于2000cm2/Vs的电子迁移率。

(4)门级电压7V

氮化镓的工艺决定,氮化镓功率器件的最大门级电压被限制在了7V,且于现有的硅驱动IC不兼容。

(二)器件工艺技术

氮化镓功率器件和硅基芯片一样,制造环节主要包括设计和外延片生长、芯片制造和封装测试。

表 2 氮化镓功率器件一般制造环节

1、设计阶段

氮化镓一般通过TCAD(计算机辅助设计技术)仿真,对结构和参数进行模拟仿真。

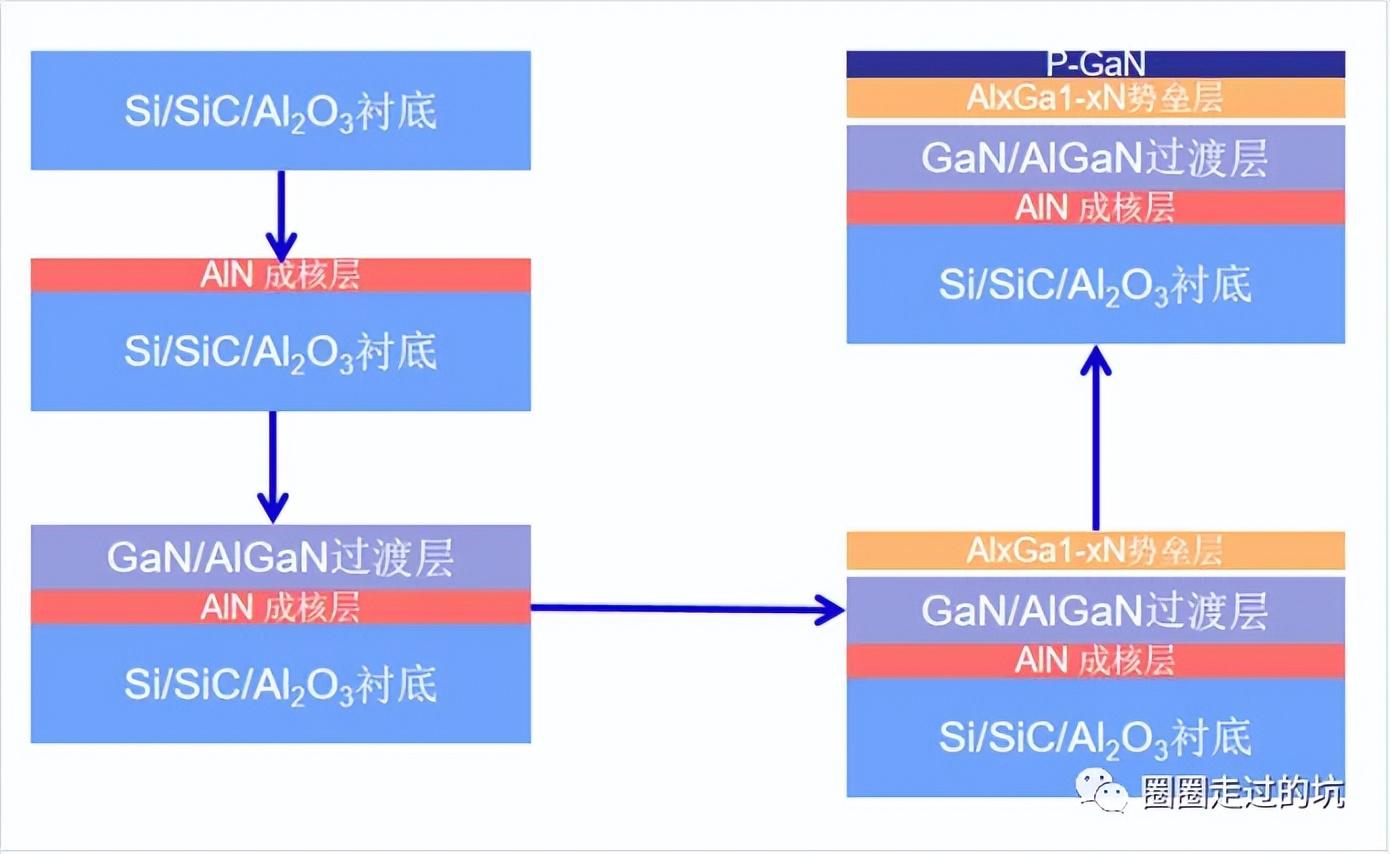

2、外延片制造流程

氮化镓外延片可在硅衬底、碳化硅衬底或蓝宝石衬底上进行生长,从成本和大批量生产考虑,外延的每一层的沉积一般采用MOCVD(金属氧化物化学气相沉积)。

图 5 氮化镓外延片制造流程

3、器件制造流程

下图是蓝宝石衬底耗尽型氮化镓HEMT器件制造的简化流程,硅基衬底的氮化镓HEMT器件工艺流程类似。

第一步是第一张光罩,是做平台型的隔离蚀刻;第二步,第二张光罩定义了源极和漏极;第三步是沉积源极和漏极的金属;第四步是玻璃和退火,形成源极和漏极金属;第五步,用第三张光罩来定义门极;第六步是做门极金属沉积;第七步是金属剥离,以形成门极金属;第八步是沉积氮化硅实现钝化和保护;第九步是使用第四张光罩来定义源极和漏极的接触;第十步是利用第五张光罩来定义场板;第十一步是金属剥离来形成场板,第十二部是沉积第二层氮化硅钝化层。

图 6 蓝宝石衬底的D-mode 氮化镓HEMT工艺制造流程

4、CP测试

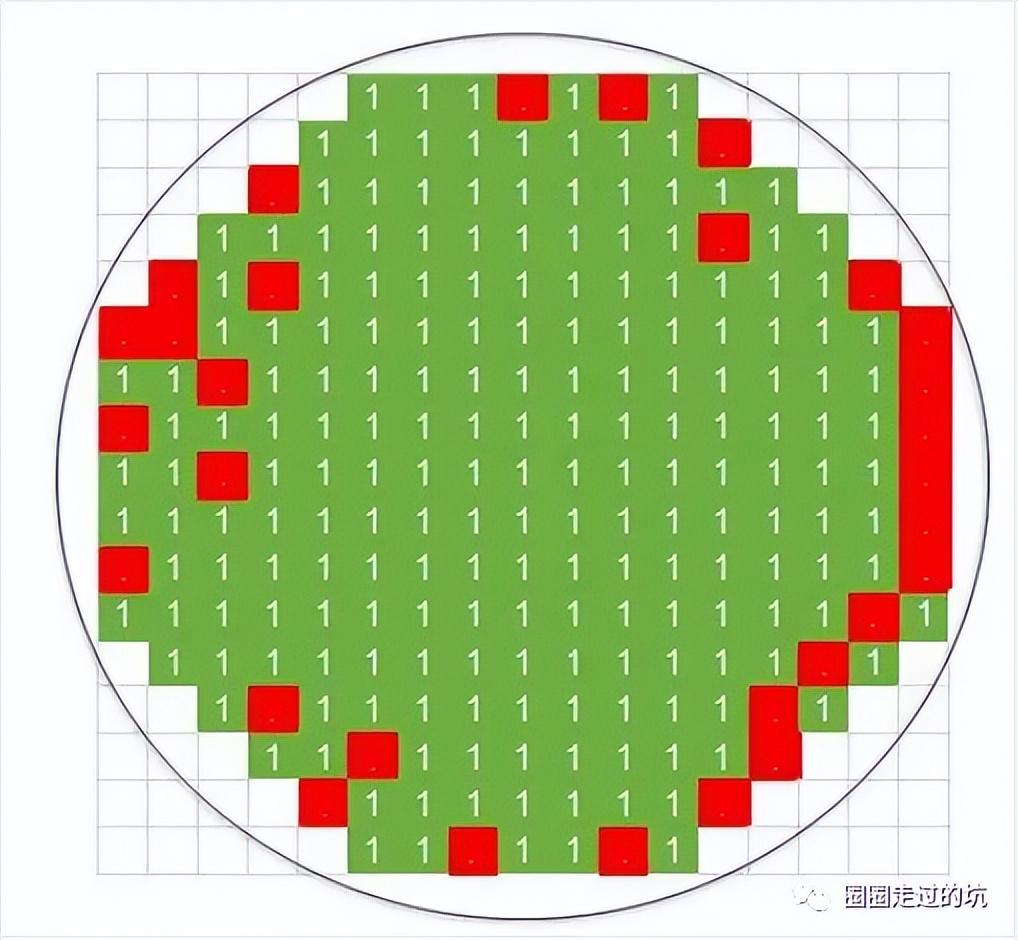

CP测试主要是通过测试室温和高温两种环境下的多种参数,来识别出晶圆上失效的芯片颗粒,并进行染色标注,不再进行后续的封装。

图 7 CP测试(红色为失效芯片位置)

5、封装

图 8 简化的封装步骤

6、FT/测试

FT(Final test)是发货前的最后一道测试,一般会在室温和高温两种环境下对器件进行测试,测试的参数主要包括Idss、Vth、Rdson以及BV(击穿电压)等。

二、器件的材料对比

(一)半导体材料特性对比

禁带宽度在2.2eV以上的半导体称为宽禁带半导体(第三代半导体)。

表 4 半导体材料的特性对比

禁带宽度:硅的禁带宽度为1.1eV,低于氮化镓和碳化硅几乎三倍。因此,氮化镓和碳化硅可以轻松支持更高电压的电路,而不能像硅一样支持较低电压的电路。

击穿电场:氮化镓和碳化硅的击穿电场是硅基的10倍以上,高击穿场使氮化镓和碳化硅能够轻松应对更高的电压。

电子迁移率:氮化镓的电子迁移率比碳化硅要高三倍,氮化镓HEMT更适合高频应用。

热导率:氮化镓的热导率为1.3 W/cmK(瓦特/厘米开尔文),还不及硅的,而碳化硅的热导率最优,在传递热负荷方面优于氮化镓和硅三倍。这种散热性能使碳化硅在高功率和高温应用中具备极大的优势。

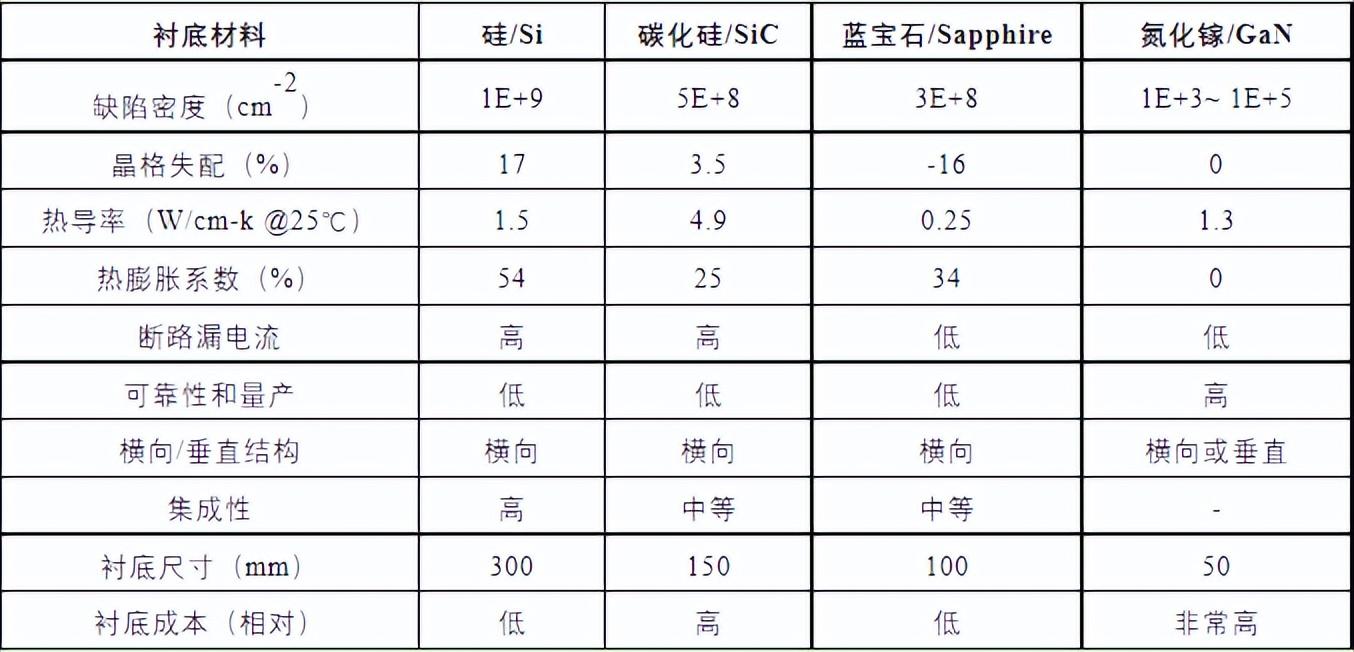

(二)衬底材料的Ga HEMT对比

表 5 不同衬底材料的GaN HEMT参数对比

因为氮化镓HEMT结构是外延结构,衬底可使用不同的材料。

附件:器件结构简介

为了更方便理解正文提及的器件结构概念,就常见的各类器件结构的缩写进行简单描述。

MOSFET:金属-氧化层-半导体-场效晶体管,简称金氧半场效晶体管,是一种电压控制器件。MOSFET有两种类型,“p沟道”和“n沟道”,这两种类型都可以处于增强或耗尽模式,因此共有四种不同类型的MOSFET。

BJT(Bipolar Junction Transistor):双极性结型晶体管,俗称三极管,一种电流驱动器件,有PNP和NPN两种类型,广泛用作放大器、振荡器或开关等。

HEMT(High Electron Mobility Transistors):高电子迁移率晶体管。

pHEMT:伪形态高电子迁移率晶体管,“p”代表伪同态。

IGBT(Insulated Gate Bipolar Transistor):绝缘栅双极型晶体管,IGBT是由MOS和PN两个基本单元构成。

HBT(Heterojunction Bipolar Transistor):异质结双极晶体管。

Triacs:三端双向可控硅。

Thyristor:半导体闸流管。

LDMOS(Lateral Diffused):横向扩散金属氧化物半导体,是高频大功率器件。LDMOS初期主要面向移动电话基站的RF功率放大器。

CMOS(complementary MOSFET):互补型MOSFET,由NMOS和PMOS组成,是集成电路的基础单元

来源:半导体材料与工艺

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码