数字射频存储器用GaAs超高速3bit相位体制ADC的设计与实现

3、工艺实现

电路采用南京电子器件研究所标准GaAsΦ76mm 全离子注入工艺实现,器件均为耗尽型器件,为非自对准常规工艺。工艺流程简介如下:N- 有源区采用大面积Si 离子注入形成,注入能量为60keV,剂量为4.3 ×1012 cm-2;N+ 区采用Si 离子选择双注入形成,注入能量分别为120,60keV,剂量均为3 ×1013cm-2;源漏欧姆接触金属采用Au/ Ge/ Ni 金属系统,栅采用常规Ti/ Pt/ Au 栅。整个流程应用金属剥离工艺,电路用Si3N4 介质实现两层金属布线隔离。严格控制栅挖槽工艺,调整器件的阈值电压到目标电压-1.3V。最终得到的芯片实际照片如图5 所示,芯片尺寸为2mm ×2mm,各功能模块均以框图标示。

4、电路测试

设计测试专用的测试盒及高速PCB 板,芯片直接装配到测试底座上,通过金丝键合至PCB 上的传输线。由于电路本身含有驱动50Ω 负载的输出缓冲驱动电路,因此,测试过程中电路存在比较大的高速开关电流。为了保证在这种电流急速开关变化下的信号完整性,需要对所有的直流馈线交流旁 路,旁路电容采用1μf 和100pf 的贴片电容,以此来稳定直流馈电的电压稳定。由于电路的量化对象是相位量,所以需要严格避免输入输出电缆给各通道所引入的额外相位误差。以每个通道输出信 号经过各自高低电平的50 %点为基准进行相位差统计。图6 为高频150MHz 输入模拟正交信号、2GHz 时钟速率下的测试结果,ADC 的输出码流速率均为1.2Gbp s。由图可见,电路各通道的相位关系正确,输出幅度在50Ω 负载上均有180mVpp 的摆幅。

图5、3bit 相位体制ADC 芯片照片

图6、150MHz 输入、2GHz 时钟速率下的输出波形

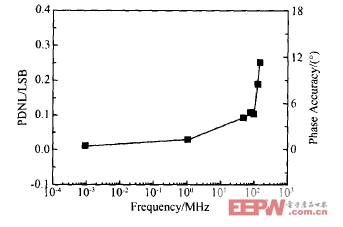

相位量化ADC 最关键的参数是相位精度随工作频率的变化情况,它决定了ADC 电路的瞬时工作带宽。在某一频率f 下,Pha(i)代表实际第i 个码元所对应的相位量,那么该频率下的相位精度PA(f)可表示为:

PA(f)= max(abs(Pha(i)- 45)) i = 1,2 ⋯,8

同传统的幅度ADC,也可以用线性度随工作频率的变化描述电路的频域性能。定义PDNL(f)代表该频率下的微分线性度,则:

PDNL(f)= PA(f)/ 45

图7 是该电路的微分非线性误差及相位精度随频率的变化特性。

图7、PDNL 及相位精度的动态性能

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码