ARM存储器之:高速缓冲存储器Cache

以上3点对实时系统来说,影响更为明显。

为了减少这种不利的影响,在ARM系统中引入了Cache内容锁定技术。这种技术允许编程人员人为地将一些关键代码或数据预取到Cache中后,通过寄存器操作对其设定一定的属性,这样当有Cache未命中发生,需要进行Cache替换时,将这些数据保护起来,使这些关键代码或数据不会被换出。

这种策略在很大程度上保证了处理器对关键代码或数据访问时的性能。

Cache的锁定操作是分组块(block)为单位进行的,它的分块方法如下。

为了叙述方便,作下述假设。

L(LengthoftheLine):Cache的基本存储单元行的大小。

A(Associativity):表示每个Cache组中的行数。

N(NumberofSets):Cache中的组数。

M表示Cache中的锁定块。

每个锁定块(lockdownblock)包括Cache每组中的一行。这样Cache中共有A个锁定块,其编号为从0到A-1。其中编号为0的锁定块中包含Cache组0中的0#行,组1中的0#行,直到组A-1中的0#行。依此类推,锁定块1包含Cache组0中的1#行,组1中的1#行,直到组A-1中的1#行。这样每个锁定块中包含了N个Cache行。

当编号为0~M的锁定块被锁定在Cache中,编号为M+1~A的锁定块可以用于正常的Cache替换操作。

| 注意 | 编程中不能将全部Cache锁定,至少要留出一个未锁定的块来支持存储器的正常操作。 |

每一个锁定块都包含有N个不同组中的Cache行。建议程序在使用Cache锁定时,使每个Cache块中的N个Cache行映射的为存储器中的连续地址。也就是说,存储器中N×L大小的联系区域被映射到Cache中锁定,这块区域是Cache行边界对齐的(如果一个Cache行包含4字节,那么被锁定的区域要是4字节对齐的,如果一个Cache行包含8字节,那么被锁定的Cache行就是8字节对齐的)。

在ARM的存储管理体系中,主要依靠系统协处理器和协处理器的寄存器c9来实现和管理Cache锁定。如果系统中使用的是数据和指令分离的Cache,那么就依靠协处理器指令MCR和MRC中的opcode>2来区分:

·opcode>=0使用数据Cache锁定寄存器;

·opcode>=1使用指令Cache锁定寄存器。

如果系统使用的是数据和指令统一的Cache,那么opcode2>要设置成0。

另外,无论是MCR指令还是MCR指令,指令中的CRm>通常设为c0。

寄存器c9有两种主要的格式:格式A和格式B。

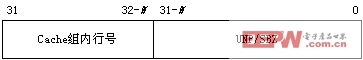

格式A的编码如图15.14所示。

图15.14格式A编码

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码