基于PCB模拟设计的良好接地指导原则

保持低阻抗大面积接地层对目前所有模拟电路都很重要。接地层不仅用作去耦高频电流(源于快速数字逻辑)的低阻抗返回路径,还能将EMI/RFI辐射降至最低。由于接地层的屏蔽作用,电路受外部EMI/RFI的影响也会降低。

接地层还允许使用传输线路技术(微带线或带状线)传输高速数字或模拟信号,此类技术需要可控阻抗。

由于“总线(bus wire)”在大多数逻辑转换等效频率下具有阻抗,将其用作“地”完全不能接受。例如,#22标准导线具有约20 nH/in的电感。由逻辑信号产生的压摆率为10 mA/ns的瞬态电流,流经1英寸该导线时将形成200 mV的无用压降:

对于具有2 V峰峰值范围的信号,此压降会转化为大约200 mV或10%的误差(大约“3.5位精度”)。即使在全数字电路中,该误差也会大幅降低逻辑噪声裕量。

图2显示数字返回电流调制模拟返回电流的情况(顶图)。接地返回导线电感和电阻由模拟和数字电路共享,这会造成相互影响,最终产生误差。一个可能的解决方案是让数字返回电流路径直接流向GND REF,如底图所示。这显示了“星型”或单点接地系统的基本概念。在包含多个高频返回路径的系统中很难实现真正的单点接地。因为各返回电流导线的物理长度将引入寄生电阻和电感,所以获得低阻抗高频接地就很困难。实际操作中,电流回路必须由大面积接地层组成,以便获取高频电流下的低阻抗。如果无低阻抗接地层,则几乎不可能避免上述共享阻抗,特别是在高频下。

所有集成电路接地引脚应直接焊接到低阻抗接地层,从而将串联电感和电阻降至最低。对于高速器件,不推荐使用传统IC插槽。即使是“小尺寸”插槽,额外电感和电容也可能引入无用的共享路径,从而破坏器件性能。如果插槽必须配合DIP封装使用,例如在制作原型时,个别“引脚插槽”或“笼式插座”是可以接受的。以上引脚插槽提供封盖和无封盖两种版本。由于使用弹簧加载金触点,确保了IC引脚具有良好的电气和机械连接。不过,反复插拔可能降低其性能。

应使用低电感、表面贴装陶瓷电容,将电源引脚直接去耦至接地层。如果必须使用通孔式陶瓷电容,则它们的引脚长度应该小于1 mm。陶瓷电容应尽量靠近IC电源引脚。噪声过滤还可能需要铁氧体磁珠。

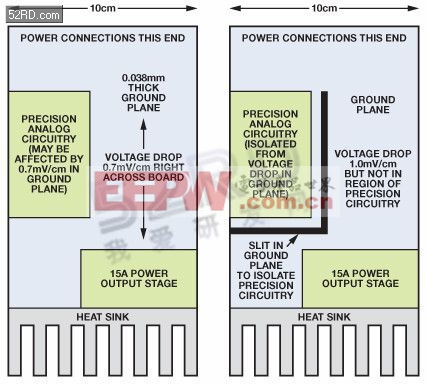

这样的话,可以说“地”越多越好吗?接地层能解决许多地阻抗问题,但并不能全部解决。即使是一片连续的铜箔,也会有残留电阻和电感;在特定情况下,这些就足以妨碍电路正常工作。图3说明了这个问题,并给出了解决方法。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码