基于FPGA 的多时钟片上网络设计

(1)缓冲部分或者全部到来的数据包,以及当下游开关可以用时,传送头部及紧跟的flit。

(2)划分路由器核心以及路由器的频率,从而支持一个多时钟的网络设计。

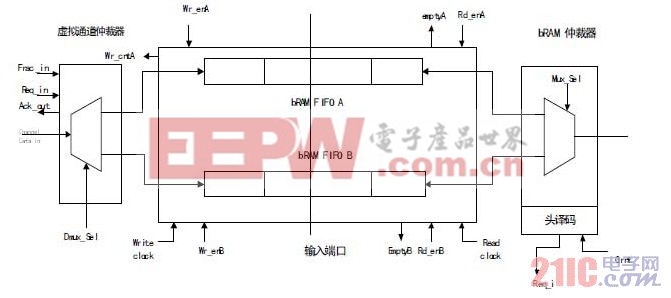

(3)通过仲裁器监察write_count 端口的信息,来实现支持可变化大小的数据包。在缓冲区有单独时钟域的情况时, 就需要一种有效的方式实施完整的或者空的逻辑。通过以下方式使控制信号同步:

(1)发送数据包粒度作为一小部分FIFO 的空间。

(2) 在一个时钟周期内, 一个连接终止之前设置flit 的尾部位。在所使用的FPGA 设计中,由于支持FIFO 的最小深度是16, 所以它适合于在虚拟直通中缓冲整个数据包。write_count 的空和满状态信号将集成在FIFO 中。在一个多数据包的缓冲区中加大存储flit 的能力,将有助于提高FIFO 的利用率。此外,获得网络的吞吐量的增益,是由于上游连续包释放缓冲区所促成的。

图1 输入端口设计图

bRAM 仲裁器: 输入端口还包含了控制逻辑作出的仲裁决定。当选择一个非空的bRAM 时, 简单的Round-robin 的方式仲裁算法将会启用。当选择bRAM时,FSM 将会送出头部flit,解码出它的目的地址,并发送相应的要求。在所设计的路由器中采用XY 路由算法将大大简化了解码器的逻辑结构。根据XY 路由算法的通行路径许可,即将释放的请求线将会减少。

头译码器:在XY 路由算法中,头数据片一开始往X 轴方向走,当到达X 轴所在的目标地址时,就会往Y方向走。所有紧随着的数据片将以流水线的方式跟着头数据片移动。这种简便的XY 路由算法适用于减化头解码器、交叉点矩阵以及中央仲裁器的逻辑结构。以上简化得逻辑结构将使FPGA 的芯片数显著减少。

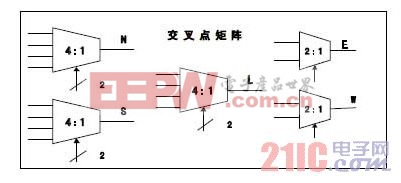

2.3 交叉点矩阵

设计一个多路交叉点矩阵, 目的是为了减少面积的使用。而另一种设计是支持复分解虚拟通道的交叉点连接。后一种方法,产生高网络吞吐量,但要增加一个重要的复杂性开关。交叉点支持并行连接,以及被用于通过中央仲裁器支持多个信号同时请求。并非所有的交叉点连接都是使用XY 路由算法。经过逻辑优化,如图2 所示设计中实施简单的4 和2 输入多路复用器开关(分别是L、N、S、E 以及W 端口)。上述优化方案减少了交叉点面积,使其使用的切片只有32 片。因此,达到路由器面积显著减小的目的。

图2 交叉点矩阵

输入端口的分配方式将采用简单的Round-robin仲裁机制。对上一次接收过的或没有用到的端口将给予最低优先级,并排在队列的最末端。将通过以下的方式提高路由器的性能:

(1)降低中央仲裁器的逻辑复杂度;

(2)尽量集中仲裁器,以减少req/grant 信号的数量。

在设计中减少逻辑复杂度以及布线, 从而减少数据堵塞,达到提高性能以及减低功耗的效果。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码