单片机与FPGA实现等精度频率测量和IDDS技术设计方案

2.等精度频率计的实现

为了减小误差,得到高的测量精度,我们采用多周期同步测量法,即等精度测量法,通过对被测信号与闸门时间之间实现同步化,从而从根本上消除了在闸门时间内对被测信号进行计数时的 l量化误差,使测量精度大大提高,是在测量领域用得比较多的的一种精度很高的测量方法。

2.1 频率测量总体设计与方案

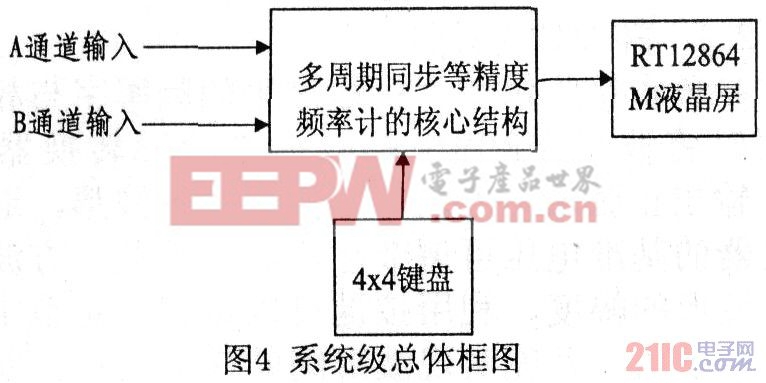

本系统主要是以凌阳单片机和FPGA为核心,多周期同步等精度测量频率计的核心结构用VHDL硬件描述语言对FPGA进行编程,实现频率、周期、脉冲宽度和占空比的测量。而单片机则作为控制部分实现了频率计的控制、扫描和显示,系统级框图如下图4:

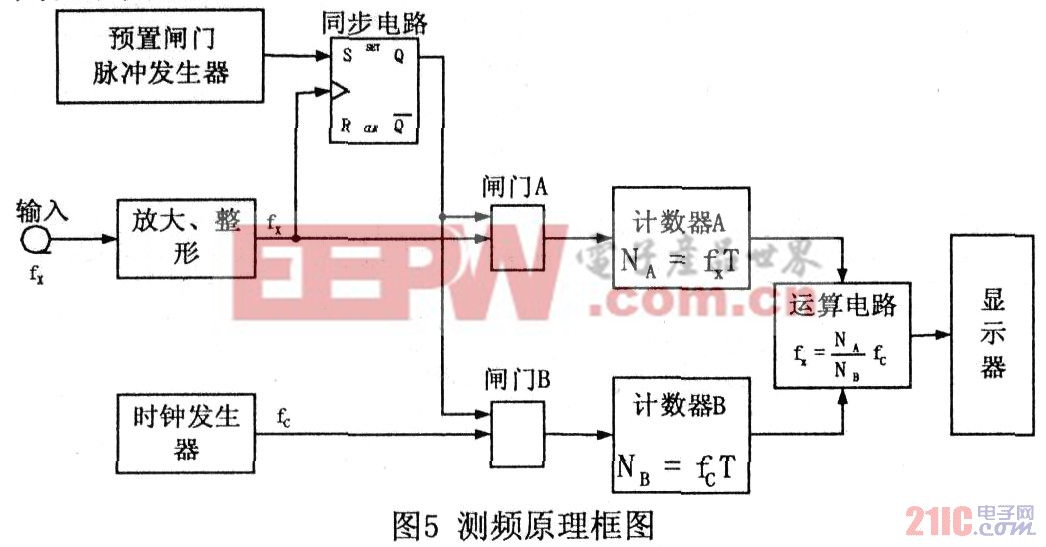

本设计频率测量方法的主要测量原理如图5所示,图中预置门控信号GATE是由单片机发出,GATE的时间宽度对测频精度影响较少,可以在较大的范围内选择,只要FPGA计数器在计100M信号不溢出都行,根据理论计算GATE的时间宽度Tc可以大于42.94s,但是由于单片机的数据处理能力限制,实际的时间宽度较少,一般可在l0~0.1s间选择,即在高频段时,闸门时间较短;低频时闸门时间较长。这样闸门时问宽度Tc依据被测频率的大小自动调整测频,从而实现量程的自动转换,扩大了测

频的量程范围;实现了全范围等精度测量,减小了低频测量的误差。

2.2 测频输入级的设计

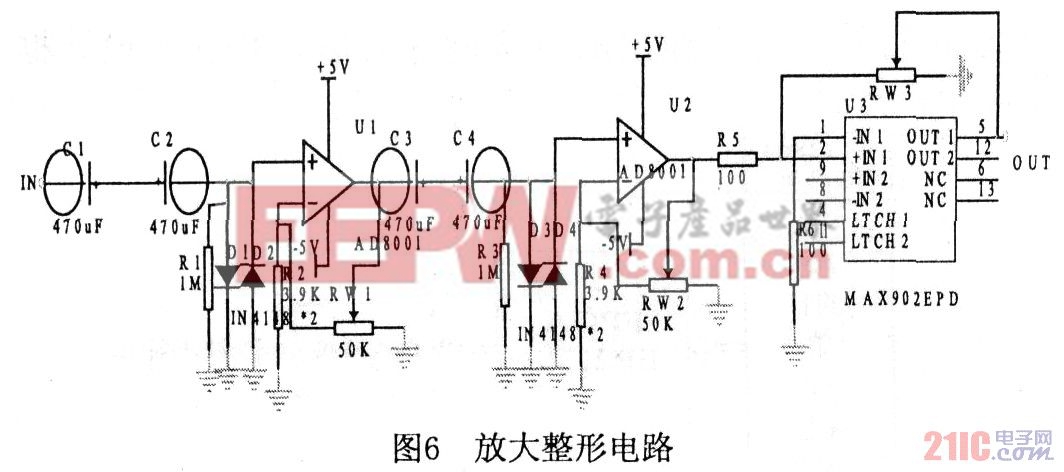

由于输入的信号幅度不确定、波形不确定、边沿不够陡峭,而FPGA只处理TTL电平的信号,因此我们必须对输入信号进行放大、整形处理。详细设计的电路图如图6所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码