基于G4平台的嵌入式VxWorks系统在雷达信号处理中的应用

在雷达数字信号处理中的应用

雷达数字信号处理主要是通过高速A /D采集雷达正交基带回波信号,然后进行数字脉冲压缩处理、杂波抑制、恒虚警和目标检测,最后把目标信息数据传送给雷达终端进行显示。采用高速A /D采集雷达回波信号,和VxWorks完成大容量数据传输和实时性处理管理,合理划分任务和安排处理时序是成功实现的关键。

基带信号采集

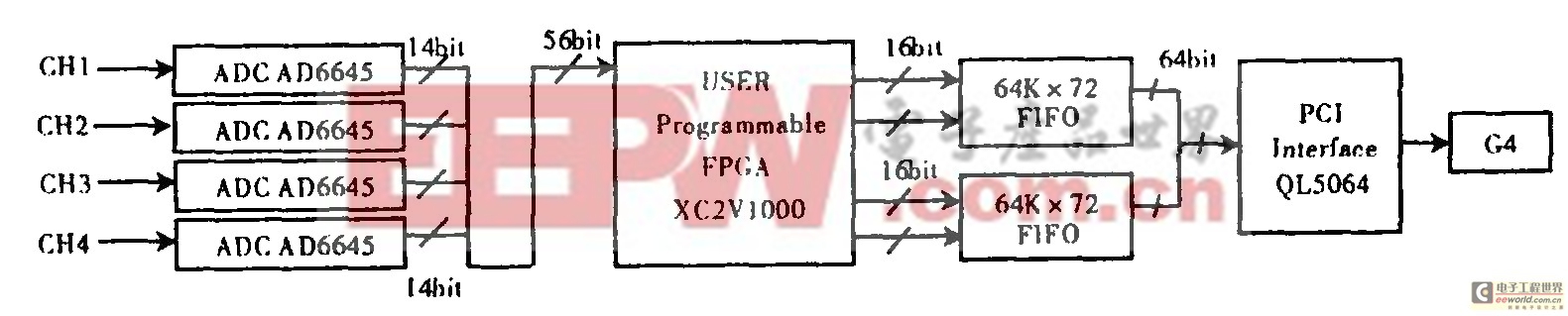

回波信号的采集使用Interactive 电路与系统公司的ICS - 554四通道14bit A /D数据采集卡,可以用内部或外部时钟采样,最小采样率30MHz,最高采样率105MHz,内部和外部两种触发信号;标准的PMC 接口,带1M逻辑门FPGA 的64bit/66MHzQL5064 PCI总线接口芯片,支持master/ target DMA突发传输方式,未使用完的FPGA资源可根据用户的需要配置使用;两片64 K ×72 bit FIFO缓存,可以编程控制进行单通道数据采集,两通道或四通道同时采集,每两通道各占一片FIFO,每片最大采样128 K点,单通道最大各采样256 K点;采用捕获和持续两种采样模式,在捕获模式每一次触发采样点数和(在FIFO缓存大小内)总的采样点数,然后向CPU发中断请求,要求从CPU从缓存中取走已采样的数据都是可编程的;为多种操作系统提供了驱动程序,如Win2dowsNT、Windows 2000、Windows XP和VxWorks实时操作系。ICS - 554的功能框图如图2所示。

图2 ICS - 554框图

在实际应用中, ICS - 554插在节点4的PMC标准接口上,采用10 kHz主触发脉冲作为外触发信号, 30MHz采样时钟, I、Q两路采样,每一个主触发脉冲采样2 048点,每一个CP I周期内要求采88个主触发脉冲周期的数据。考虑到每一路F IFO最大只能采256K点和DMA 方式下PC I总线的实际传输率,保证每一个CPI的数据不会丢失和FIFO不会溢出,采用每42个主触发脉冲周期就请求CPU开始接收在F IFO 缓存中的数据,先接收完F IFO1 中的数据,再接收F IFO2 中的数据,以后循环进行数据传输,直到禁止A /D采样为止。

时序安排

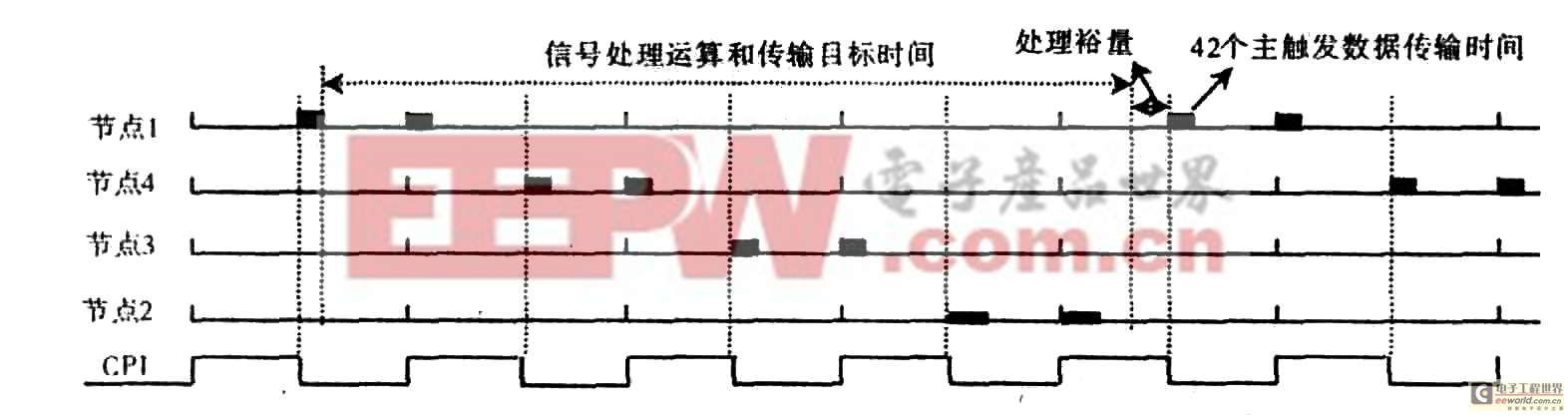

信号处理系统接收雷达终端发来的控制命令和正交回波信号经过A /D采样后的数字信号,雷达终端在CP I信号的下降沿通过VME总线发当前CPI信号的控制命令到G4板的VME内存映射空间,节点1把这些控制命令码值拷贝到全局共享内存,控制命令码值包括模式码,探测距离码等值;然后通知节点4取出当前模式码,节点4根据模式码对ICS- 554进行配置和允许ICS - 554开始采数并存入FIFO中。ICS - 554每采完44个主触发脉冲周期的数据后,向节点4发中断请求,节点4接到请求后通过节点1的全局共享内存查询当前控制命令,接着根据模式码配置 QL5064的DMA控制器。目标内存是节点1上的共享内存,启动DMA传输,把A /D采样存入FIFO 中的数据传给节点1, DMA传输完成后,节点4向节点1发出中断请求,节点1响应请求后,查询全局共享内存的控制命令,根据模式码开始进行脉冲压缩、杂波抑制、恒虚警和目标检测等信号处理。信号处理完后通过VME总线把目标信息数据传送到VME空间,通知雷达终端取走目标和状态信息;其它节点的数据也是通过节点4以DMA方式传到内存中进行处理,处理方法与节点1相似,只是节点2、3和4的目标信息数据先传到节点1,然后由节点1通过VME总线传给雷达终端,每个节点都独立处理一个CP I周期的数据。从A /D FIFO缓存中传数到各节点的顺序和信号处理顺序时序如图3所示。

图3 时序图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码