一种基于FPGA的真随机数发生器设计与实现

定性分析如下:将序列的每位看作是一个随机的二进制变量X,定义b是序列的偏置。即

b=|P(X=1)-1/2|=|P(X=0)-1/2| (2)

根据Piling-up引理,输出序列的偏置是:

)时成立。简而言之,异或运算显著地减小了独立输入序列的偏置。假设n=16且所有bi=1/3,那么b=0.000 761可以忽略不计。

2.3 后续处理模块对统计性能的改善

由上一节的分析可知,增加振荡器数量是改善序列统计特性的有效方法。但前提条件是各个振荡器相互独立。当振荡器数量过多时位置约束很可能与相互独立的要求相互矛盾。因为高速的振荡信号往往发生相互串扰的情况,并且消耗更多资源和功耗,所以有必要在保证TRNG包含一定数量的振荡器的前提下,引入后续处理模块。从而达到消耗资源较少,序列性能较好的目的。

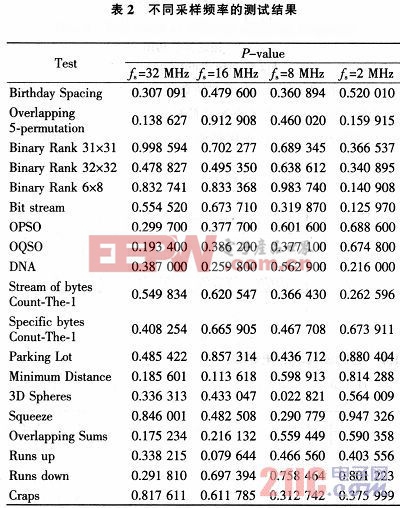

本项测试以19组振荡器作为TRNG的随机源,输出序列与PRBS模块输出进行异或运算,然后分别使用32,16,8,2 MHz的采样时钟采集数据。将数据送入测试程序进行测试以后,结果如表2所示。

可以看出,TRNG生成的随机序列全部达到了预定的性能指标。同时不难发现,采样时钟频率对TRNG的输出统计特性是有影响的,当采样频率逐渐降低时,TRNG的随机性能逐步提高。出现这种现象是由于采样频率越高,就与振荡频率越接近,二者的相位偏移干扰了随机信号的获取影响了统计特性。

3 结束语

本文尝试了一种纯数字形式的真随机数发生器结构,规模较小、易于移植。电路包含两个振荡环,分为自由振荡和锁存至双稳态两个工作状态。利用振荡环之间的相位偏移和抖动以及双稳态器件的亚稳态作为随机源。本文探讨了振荡器数量对序列统计特性的影响,并在加入后续处理模块的情况下试验了多种采样频率,经测试随机序列完全符合预定指标。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码