一种基于FPGA的真随机数发生器设计与实现

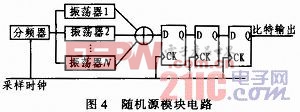

1.4 随机源模块的电路设计

各个振荡器的输出经过异或运算可以增加随机性,而亚稳态的传播会造成后续电路的错误动作,因此使用同步器将异或后的随机序列与后续电路隔离开来,同时也方便采集稳定的输出序列做性能分析。此处采用了三级寄存器的同步结构,由MTBF(Mean Time Between Failure)的定义可知,平均需要经过数百年时间才会发生一次亚稳态通过同步器向下传播的事件,因此是满足设计要求的。该模块电路图如图4所示。

1.5 后续处理模块的设计

理想情况下,D触发器所采集的信号具有随机的统计特性,可是FPGA内部电路不可避免地会受到温度漂移、电压抖动等不良因素影响,从而导致采样得到的随机信号中存在偏置,影响结果的统计特性。所以在采样得到随机序列后要对数据进行消偏处理,使0和1出现的概率相当。

本设计采用16位最大长度二进制伪随机序列(Pseudo Random Binary Sequence)的输出与采样得到的随机序列进行异或运算作为后续处理,PRBS产生电路消耗资源少并且使用线性反馈移位寄存器实现,非常适合于在FPGA上实现。它的生成多项式是:

![]()

多项式表示如图5所示。

2 TRNG的FPGA实现与测试

整个TRNG的实验环境由外部时钟源、FPGA开发板以及逻辑分析仪组成。TRNG采用Xilinx公司的Virtex-5系列中的XC5VLX110作为物理实现平台,外部时钟频率为64 MHz。由FPGA产生的随机数据,经逻辑分析仪采集后,使用DIEHARD battery of tests of randomness随机数测试程序进行测试,检验随机序列的性能。

DIEHARD测试是由16项测试组成的用来度量随机数发生器性能的一组统计学测试,它由George Marsaglia开发并于1995年首次发布。DIE HARD的测试结果叫做P-value,它由方程P-value=Fi(X)计算得到,其中Fi试图建立样本X在0和1间服从均匀分布的分布函数。因为Fi是渐进逼近的,它在尾部的近似效果变差,所以数值接近0或1的P-value在真随机序列中极少出现。当被测序列随机性能很差时,会有很多P-value的值是精确到小数点后数位的0或者1,例如1.000 000。需要强调的是,P-value等于1.000 000或0.000000是序列为真随机序列的充分不必要条件。

2.1 FPGA位置约束

为保证每个振荡器中的两个独立振荡环的理论振荡周期相同,以便更容易在锁定期间产生亚稳态,加大噪声对输出电平的影响,同时尽量让各个振荡器的输出在进行异或运算前延迟不出现太大偏差。所以对TRNG中的振荡环进行位置约束:将振荡环中的反相器约束在左右相邻的逻辑单元(Slice)中,让各个振荡环分别约束在上下相邻的逻辑单元中。

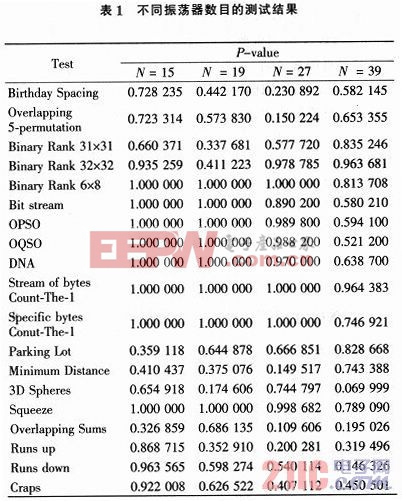

2.2 振荡器数目对统计特性的影响

在32 MHz的采样频率下,分别以15组、19组、27组和32组振荡器作为TRNG的随机源,随机序列经过同步器后不与PRBS运算直接输出。将采集到的随机序列送入测试程序进行测试以后,其结果如表1所示。

可以看出,振荡器的数目直接影响随机源模块产生序列的统计性能,振荡器数目越多,TRNG输出序列的随机性越好。但是如果振荡器的数目太多,会消耗过多的硬件资源,功耗也过大。因此,不宜通过单纯地增加振荡器数目的方法提高随机序列的性能。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码