基于FPGA的部分响应CPM信号解调器的设计

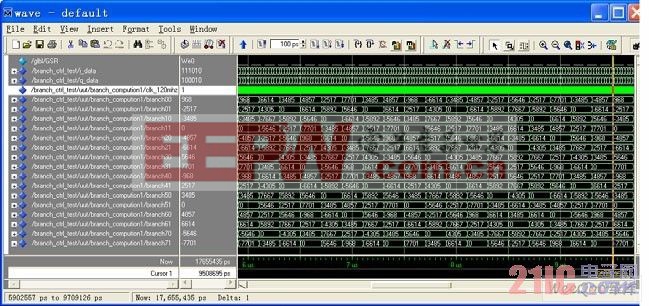

仿真中选择二进制,关联长度L 取2,升余弦脉冲的调制方式。仿真中波特率为5 MHz, 采用8 倍采样,系统时钟为120 MHz。假设输入到调制器的双极性比特流为{ } n b :1,1,1,-1,1,1,-1,-1,1,1,1,-1,1,1,-1,1……分支度量仿真结果如图3 所示。

图3 分支度量仿真结果

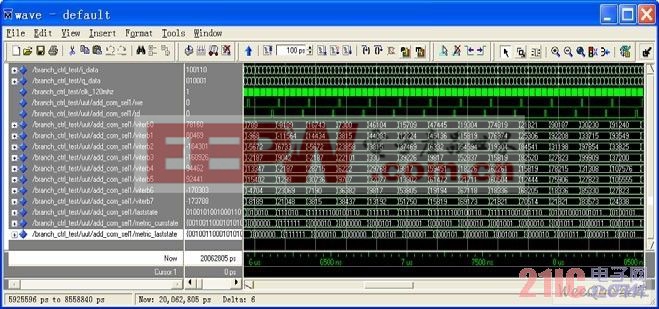

加比选模块仿真结果如图4 所示。

图4 加比选模块仿真结果

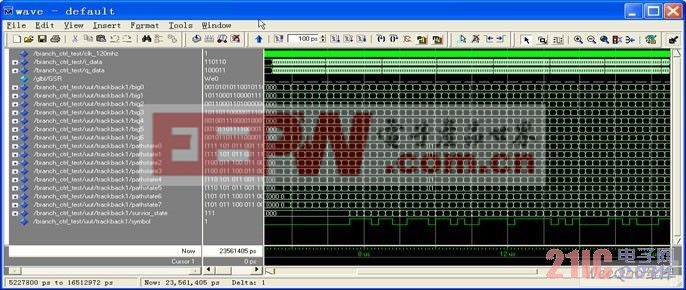

幸存路径存储和判决输出模块仿真结果如图5 所示。

图5 幸存路径存储和判决输出模块仿真结果

译码码字:1,1,1,-1,1,1,-1,-1,1,1,1,-1,1,1,-1,1……当调制信号不加高斯白噪声时,实现了误码率为0 的解调。仿真结果表明这里所设计的性能达到设计的要求。

4 结语

文中主要设计了该二进制2RC CPM 信号基于FPGA 的解调器。该方法针对Viterb 译码方法,提出了一种新的防止路径度量值溢出方法。该设计的优点是:幸存路径存储器中存入的只是路径信息,不需要存储路径度量值,节省了存储空间;当译码输出时只需要读出最大路径度量值的状态所对应的幸存路径存储单元的最低位状态值,提高了译码速度。该方法有效地防止路径度量值溢出。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码