基于FPGA的部分响应CPM信号解调器的设计

2 CPM 解调模块的原理及其实现

2.1 解调器实现原理

对CPM 信号的接收、解调,常采取的步骤为:解调-最大似然序列估计-Viterbi 译码-判决。首先将接收到的复包络信号分为I,Q两路,下变频为基带信号,分别与cos(ψ (t, a))和sin(ψ (t, a))相关后相加,从而得到节点的度量值。对于t时刻每个状态,可以根据其输入值的不同,计算来自前一级节点的两条路径的路径度量,并分别加上前一级节点的节点度量,然后从中选择一个最小的度量值作为节点度量,并存储前一级节点的信息。

2.2 解调器实现框图

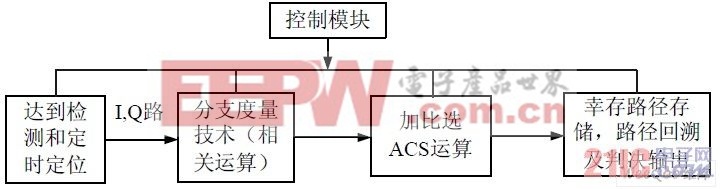

这里仿真采用二进制2RC 的调制方式,根据Viterbi 译码方式可知,调制信号共有8 个状态,将这些状态分别编码为000,001,010,011,100,101,110,111。输入数据与状态间转移关系见表1。笔者在设计中将其分为四个模块:分支度量模块、加比选模块、回溯模块和控制模块。其结构设计如图2 所示。

图2 解调过程

(1)分支度量模块

此模块根据输入数据计算分支度量值。在FPGA设计中,预先将每种基准状态抽样时刻的值存入STD 寄存器中,在计算分支度量时通过查表得到基准状态的值。将输入I,Q 两路数据进行串/并转换,得到一个码元持续时间内的调制信号后,与每种基准状态的抽样值相乘并相加,从而得到I,Q 两路的路径度量值。最后将I,Q 两路度量值相加,便可以得到各状态的分支度量值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码