一种基于FPGA的电子稳像系统的研究与设计

1.5 VGA接口控制器

标准的VGA(640×480,60Hz)接口需要提供以下几组信号:3个RGB模拟信号、行同步信号HS和场同步信号VS。它的信号时序如图6所示。

图6中VS为场同步信号,场周期为16.683ms,每场有525行,其中480行为有效显示行,45行为场消隐区,场同步信号每场有一个脉冲,该脉冲的低电平宽度为63μs(2行)。行周期为31.78μs,每显示行包括800点,其中640点为有效显示区,160点为行消隐区(非显示区)。行同步信号HS每行有一个脉冲。该脉冲的低电平宽度为3.81μs(即96个脉冲)。因此,VGA控制器的任务就是按要求产生所需要的时序。

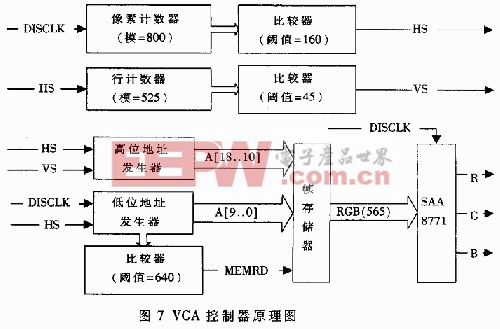

DISCLK为视频显示时钟,频率为25MHz,首先输入到模等于800的像素计数器中,输出的计数值与一个预先设好的比较器进行比较,当计数器的值大于160时,输出高电平,反之输出低电平,作为行同步信号;同理,利用一个模等于525的计数器对行同步信号进行计数和一个阈值为45的比较器可以产生所需要的场同步脉冲VS。

产生的行、场同步信号和像素显示时钟分别被送到两个地址发生器中,产生所需要的控制帧存储器的地址信号。由于前面介绍的帧存控制器中采用为每行数据提供1024个存储空间的办法,因此在数据读出时也要进行相应管理。低位地址发生器产生的地址数据与一个比较器进行比较。当地址小于640时,帧存储器的读信号MEMRD位低电平有效,否则无效,这样有效像素数据就被完整地提出。由于VGA是一个模拟的接口标准,RGB彩色信息需要输入模拟量,因此帧存储器输出的数字信息还要经过D/A变换。系统先用飞利浦公司出品的TDA8771AH,它内部集成了三个视频D/A转换器,基于电阻网络架构,转换速率最高可达35MHz。由于它专用于数字电视、视频处理等相关领域,因此使用十分简单,只需要提供24bit数字信息和一个转换时钟即可。VGA控制器原理图如图7所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码