一种基于FPGA的电子稳像系统的研究与设计

1.3 帧存控制器

帧存储器是图像处理器与显示设备之间的通道,所有要显示的图形数据先存放到帧存储器中,然后再送到显示设备进行显示,因此帧存储器的设计是图形显示系统设计的一个关键。传统上,可以实现帧存储器的存储器件有多种,如DRAM、SDRAM及SRAM等。DRAM、SDRAM属于动态存储器,容量大、价格全家但速度较慢,且在使用中需要定时刷新。对于基于FPGA的视频处理器,需要设计专用的刷新电路,增加了系统设计的复杂程度。SRAM速度高、接口简单、容量较小。随着集成电路技术的不断发展,容量不断增大,价格也不断下降。在需要高速实时显示的视频处理系统中的使用越来越普遍。

帧存控制器的设计对于实现两种不同视频系统之间的图像信号的存储、采集和显示显得非常重要。为了保证数据处理与采集的连续,设计中使用了两组帧存储器(FRAM1、FRAM2),由于数字化的图像每帧大小为640×480=307200(16bit)共300K×16bit的数据量,笔者使用每组512K×16bit的静态存储器,存储时间为12ns,可以保证快速地读出和写入图像数据。图3为帧存控制器的逻辑框图。

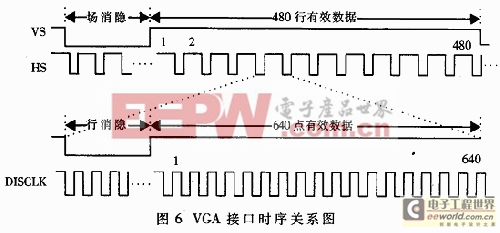

由于输入信号为隔行扫描的图像数据,显示输出需要逐行扫描数据,因此数据存入帧存储器时需要进行处理。设计中采用场合并行法,将两场的数据写入一个帧存中,构成一幅完整的逐行扫描图像,系统利用VREF信号对此进行控制,产生的帧切换控制信号控制数据在两个帧存中的切换。当VREF信号有效时,表明新的一场开始了,此时无效行计数器开始工作,控制不需要采集的图像行,计数到阈值后,有效行计数器开始工作,控制所要采集的图像行,并发出高位地十信号A[18..11];同样,当HREF有效后,无效像素计数器开始计数每行中的无效像素,然后有效像素计数器开始计数需要采集的行听有效像素;每次计满640个像素后,等待下一次有效行信号的到来,同时将有效行计数器加1。由于系统选用的帧存容量较大,因此利用ODD的反相信号作为帧存地址的A10,为每行图像提供了1024个存储空间(实际使用640个),可以简化数据写入与读出的控制电路。隔行的视频信号就会被逐行地存储到帧存体中。总线隔离与控制电路用来完成数据在帧存中的写入与读出的同步。由于采用SRAM作为帧存体,有效像素的写入与后续视频接口的读出不能在一个帧存体中同时进行,系统采用双帧存轮流操作的方法,系统采用双帧存轮流操作的方法:当数字化后的图像信息写入其中的一个帧存时,帧存控制器将另一个帧存中的像素顺序读出,送到显示设备,反之亦然。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码