可重构技术及基于FPGA的可重构智能仪器设计

2.2 控制核

在基于 FPGA 的可重构智能仪器中,EP2C35F672C6 是整个系统的核心,为了实现FPGA 与其他芯片、器件的正确通信、数据交换,需要在FPGA 上配置Nios II 软核处理器以及其 他控制器核。

(一)Nios II 嵌入式处理器的设置。首先在Quartus II 下建立一个Project,在SOPC Builder 中选择组件列表中的Nios II Processor-Altera Corporation,考虑到芯片的性能以及资 源利用率,选择Nios II/s(标准型)CPU,在Cache Tightly Coupled Memories 标签下设置 Instruction Cache 为4KB。在JTAG Debug Module 标签下选择Level 3,可设置2 个硬断点、 2 个数据触发、指令跟踪和片上系统。整个Debug 模块将占用2400~2700 个LE,4 个M4K。

(二)添加SDRAM 控制器内核。在SOPC Builder 组件选择栏中选择Avalon Components→Memory→SDRAM Controller,加入SDRAM 控制器核,。在Data Width(数据 总线宽度)下拉列表框中选择16Bits,其余设置不变,因为都满足SDRAM 芯片IS42S16400 的参数要求。Timing 选项卡的参数也满足芯片要求,不必修改。

(三)添加 Flash 控制器。在对硬件系统进行编程控制时,Flash 用于存储应用程序。 在SOPC Builder 的组件选择栏中选择Avalon Components→Bridge→Avalon Tri-State Bridge, 加入Avalon 三态总线桥; 在SOPC Builder 的组件选择栏中选择AvalonComponents→Memery→Flash Memery(Common Flash Interface),添加CFI 控制器。

(四) 定时器设置。在SOPC Builder 组件选择栏中选择Avalon Components→Other→Interval timer,加入定时器核。定时器的硬件配置选项会影响定时器的 硬件结构,SOPC 提供了简单周期中断配置、完全功能配置和看门狗配置三种硬件配置。

(五)添加 SPI 核。采用的A/D 转换芯片和D/A 转换芯片都是基于SPI 总线进行数据 传输的,要实现Nios II 系统对转换芯片的控制必须添加SPI 核。在SOPC Builder 组件选择 栏中选择Avalon Components→Communication→SPI(3 Wire Serial),配置SPI 核。由于用到 的模数转换芯片AD7810 和数模转换芯片AD5611 对于Nios II 系统来说都是从SPI 器件, 所以在FPGA 中添加两个主SPI 核分别控制A/D 和D/A 转换芯片。

2.3 可重构配置文件生成

在完成可重构智能仪器的各个控制器核之后,要生成相应的配置文件,才能配置FPGA 芯片,使其实现各种功能。

配置是对 FPGA 的内容进行编程的一个过程。目前大部分FPGA 都是基于SRAM 工艺 的,而SRAM 工艺的芯片在掉电后信息就会丢失,需要外加专用配置芯片,在上电时,由 这个专用配置芯片把配置数据加载到FPGA 中,之后FPGA 就可以正常工作了。

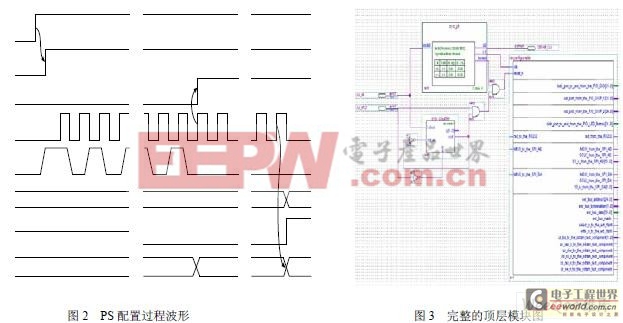

在被动模式(PS)方式下,FPGA 处于完全被动的地位。FPGA 接收配置时钟、配置命 令和配置数据,给出配置的状态信号以及配置完成指示信号等。PS 配置时序如图2 所示:

根据 SOPC Builder 中对FPGA 添加的各种控制器核,利用Quatus II 软件例化Nios II 处 理器,生成了完整的FPGA 内部顶层模块图,如图3 所示。然后利用引脚规划器Pin Planner 对其进行引脚分配。最后用进行Compilation,生成.sof 和.pof 配置文件,完成硬件设计。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码