基于通道控制的双余度DSP设计与实现

双余度DSP模块硬件设计

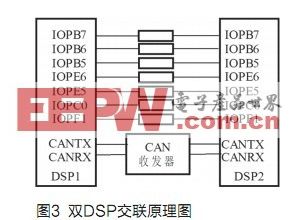

双余度DSP模块是本设计的重点,其硬件原理如图2的双余度DSP模块。它由双DSP核及通道控制逻辑两部分组成。其中DSP1为主CPU,DSP2为辅CPU。当系统上电启动后主CPU通过I/O口通知辅CPU进行自检并采集其自检信息,同时当主CPU的EEPROM内容发生改变时,主CPU通过CAN总线发送相应的数据给辅CPU以更新辅CPU的EEPROM内容,如图3所示。图中CAN收发器为两个对连的CAN总线收发器,负责实现双机间系统即时信息的传送,并存储于各自对应的EEPROM中,供维护和查询。

通道控制逻辑决定着整个系统的当前工作CPU,即当其中一个CPU被认为有故障时,通道控制逻辑将主动或是被动地切换到系统认为没有故障的CPU,或决定由其中的一个CPU强制工作。通道控制逻辑的硬件原理如图4所示。所谓的主动切换是指当主DSP通个自检发现自身有故障(包括其对应的通道故障),而其程序能正常工作的情况下,由其程序产生的通过控制I/O口的逻辑电平而产生的通道切换。被动切换是指非DSP自检的因素产生,而是由于通道控制逻辑本身硬件故障引起的通道意外切换。通道控制逻辑硬件由门电路组成,能有效地防止双机的抢权问题。同时控制逻辑返回给两个DSP一个“CTL_BACK”状态回读信号,用于判断当前的通道情况。

主DSP通过控制输入端口的逻辑状态来使能相应的通道,只有当两个控制端同时有效时选通主通道,此时主DSP工作。其他任何状态都将打开辅通道。可以有效避免由于主控DSP I/O口失效而产生不能切换的后果。同时主DSP不断检测“CTL_BACK”状态回读信号的状态,否则将产生被动切换,说明通道控制逻辑硬件故障。辅DSP上电后不断检测“CTL_BACK”状态回读信号,若检测到为有效,则说明通道已经切换到了辅通道,辅DSP开始工作。

应用处理及其输出单元

针对于不同的应用其处理及输出单元具有各自的特殊性,本应用要求输出多路电压控制信号,主要由带SPI接口的16路模数转换芯片及驱动电路组成,并通过DSP的I/O口控制D/A的复位、清零等操作。

系统软件

系统软件设计主要基于CCS2.2 Code Composer Studio集成开发环境,主程序采用汇编语言编写,软件调试及仿真完成。控制板DSP软件流程框图如图5所示,系统软件主要实现双机间的通讯及故障判别并切换,并完成控制任务处理。包括主DSP软件及辅DSP软件两部分,其中任务控制处理功能部分是相同的,重点在于双机间的交互问题。

在双机交互的切换问题中,起主要作用的是通道的切换,当前打开的通道具有最高优先权,不管产生DSP切换的原因是什么,其最终的结果都将是当前只有一个通道是打开的,通道的切换可能是由主DSP程序主动控制而切换,或是控制逻辑本身的硬件原因,但是只有这个对应的打开通道的DSP能真正控制外部的输出,这即所谓的通道分用。切换依据如图5所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码