采用FPGA设计SDH光传输系统设备时钟

系统时钟工作在自由振荡模式时,由高频时钟直接自由分频得到系统时钟。

根据ITU-T G.813建议要求,SEC带宽较窄(-3db带宽在1~10Hz内)。在逻辑滤波器模块,采用FPGA内部的数字逻辑实现二阶线性滤波器,满足了SEC噪声传递特性的要求。为了灵活应用,滤波器的环路带宽可以通过微处理器接口进行灵活调整。当参考源切换时,通过滤波器的平滑设计,保证了频率控制字缓慢变化,可靠地实现了参考源的平滑切换。

数控时钟产生器模块由高频时钟在频率控制字的作用下进行受控分频得到。为了减小数控时钟产生器输出时钟在受控分频过程中产生的数字相位噪声,TSP8500芯片设计时采用了独特的“微小相位调整技术”,使数控时钟产生器输出时钟的Cycle-Cycle抖动仅0.4ns。

SEC一般都采用主备备份设计。由于SEC本身的带宽较窄,俘获速度较慢,当主备SEC跟踪同一路参考源时,无法时刻保持主备SEC相位同步。设计中增加了主备互锁模块,保证了主备相位的快速同步。主备互锁模块也由ADPLL实现,但其环路带宽设计的较宽,俘获速度很快,足以保证主备相位准确同步。SEC工作在主模式时,主备互锁模块直接锁定本板的全数字锁相环ADPLL输出的时钟;而当SEC工作在备模式时,主备互锁模块锁定对板送来的系统时钟RDSYSCLK。

主备互锁模块输出的时钟,仍然有0.4ns的相位抖动。在这里通过FPGA自带的PLL(锁相环2)进行相位平滑。

主板的系统帧头直接由主板的38.88MHz时钟自由分频得到。而备板的系统帧头,则由本板的系统时钟在主板送来的同步帧头受控下分频产生。由于主备系统时钟的相位同步了,所以保证了系统帧头的相位同步。

1.2 外同步时钟的设计实现

芯片输出的外同步时钟ext_clk_out由一路ADPLL实现。

外同步时钟可以从输入时钟或系统时钟中任选一路作为参考时钟进行跟踪;通过

外同步时钟环路的滤波设计,也由FPGA内部的数字逻辑直接实现,但是环路带宽设计得比较宽。当进行参考源切换时,ADPLL会短暂地进入保持工作模式,保证了输出时钟的稳定。

由于外时钟频率为2.048MHz,不能由311.04MHz时钟整数分频得到,所以数控时钟产生器模块采用了小数受控分频设计。由于采用了小数分频,数控时钟产生器输出的外同步时钟的相位抖动为0.8ns。

鉴于FPGA的PLL资源限制,外同步时钟没有采用APLL进行滤抖,而是直接由数控时钟产生器输出。但是输出时钟的相位抖动也远远能够满足小于0.05UI的要求。

2 输出时钟的性能指标测试

对TSP8500芯片输出的系统时钟和外同步时钟的各项指标进行了测试。下面主要给出时钟的抖动特性以及锁定模式下SEC的相位漂移特性和保持模式下SEC的相位漂移特性。

2.1 输出时钟抖动特性

将高速示波器设置为“长余晖”模式,测试TSP8500输出的系统时钟sysclkout和外同步时钟ext_clkout的信号波形,得到输出时钟的P-P抖动特性。其中sysclkout时钟的P-P抖动小于100ps;ext_clkout时钟的P-P抖动小于2ns。

2.2 SEC的相位漂移特性

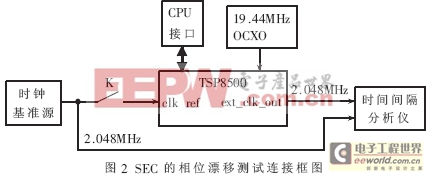

测试方法如图2所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码