基于DDS的信号模拟器设计

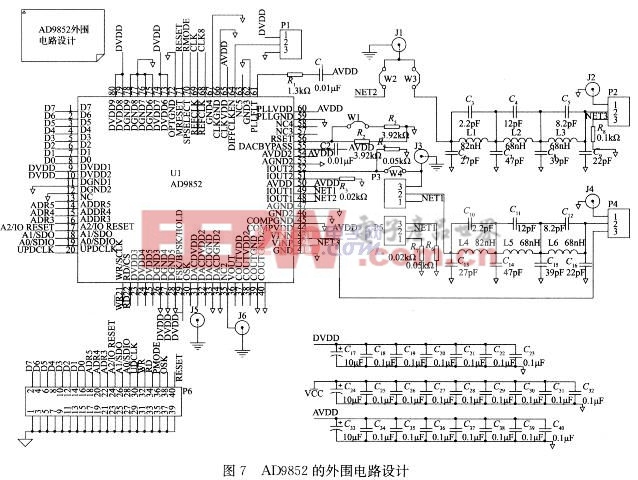

图7为在DDS的信号发生器中AD9852的外围电路设计。

2 测试结果

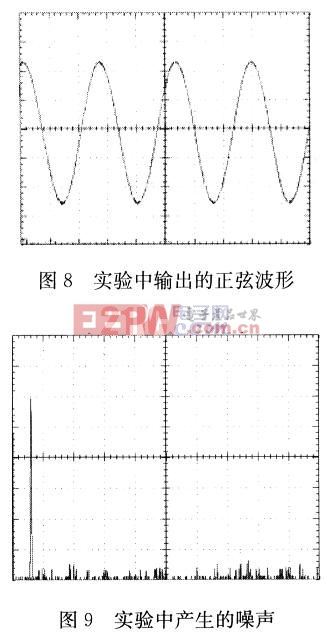

本文设计的DDS信号模拟器输出最大频率受到D/A转换器输出建立时间的限制,因为外接存储器的数据读取时间为15 ns,可编程逻辑器件FPGA的最大时钟频率可达120 MHz。相位累加器的字长为31位,用于寻址波形数据存储器的地址信号为13位;编程产生的正弦波的输出的频率范围是0~120 MHz。其中产生的正弦波如图8所示,但是随着时间的增长,噪声会加大如图9所示。

3 结束语

本文结合DDS信号模拟器的工作原理从理论和实际2个方面,对直接数字频率合成技术(DDS)进行了研究。

首先通过对DDS信号模拟工作理论分析,再通过对DDS射频信号产生电路的研究实验使得微波信号和变频信号在微波变频器上混频,产生载频信号,再者使得调制包络信号和调制脉冲对载频信号进行调制,形成雷达信号,然后经天线输出。最后结合理论分析的结论,通过测试实验得出了系统的性能以及带宽线性调频和带宽10点跳频的过程最终输出了雷达视频脉冲输出波形,基本实现了设计的要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码