基于DDS的信号模拟器设计

第2路是由DDS调频及频率捷变信号产生器产生各种调频(普通调频、线性调频和非线性调频等)和频率捷变信号,DDS工作模式为单音频工作模式时,通过改写频率控制字可实现跳频和频率捷变和频率调制,工作模式为线性调频模式时,通过设定起始频率、频率部进和扫描时间,可实现线性调频。

第3路是由DDS编码及调制波形产生器产生各种编码和调制信号,DDS的一个显著的特点就是在数字处理器的控制下能够精确而快速地处理频率和相位。DDS允许用户对通过改写相位偏移控制字可实现相位的任意控制,码元的产生完全由软件灵活控制,可产生包括二相编码(巴克码、伪随机码)、多相制编码等,并经倍频、滤波和放大后形成调制包络信号。

最后来自第l路微波信号和第2路的变频信号在微波上变频器混频,产生载频信号,来自第3路的调制包络信号和脉冲产生器产生的调制脉冲对载频信号进行调制,形成雷达信号,最后经天线输出。图4、图5为最后输出的波形。

1.6 DDS硬件设计

1.6.1 硬件电路的组成

图6为DDS模拟器硬件电路的组成原理。该信号模拟器主要由6个部分组成:电源电路、串行接口电路、下载电路、FPGA控制电路、AD9852外围电路以及滤波电路。

1.6.2 AD9852外围电路

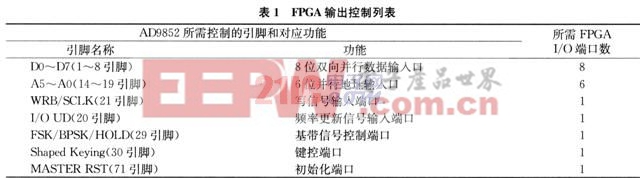

如表1所示,在并行工作模式下,FPGA主要实现对AD9852以下各引脚的控制。

AD9852内部包括1个具有48位相位累加器、1个可编程时钟倍频器、1个反sinc滤波器、2个12位300 MHzDAC、1个高速模拟比较器以及接口逻辑电路。其主要性能特点如下:

(1)高达300 MHz的系统时钟;

(2)能输出一般调制信号,FSK、BPSK、PSK、CHIRP、AM等;

(3)100 MHz时具有80 dB的信噪比;

(4)内部有4*到20*的可编程时钟倍频器;

(5)2个48位频率控制字寄存器,能够实现很高的频率分辨率。

(6)2个14位相位偏置寄存器,提供初始相位设置。

(7)带有100 MHz的8位并行数据传输口或10 MHz的串行数据传输口。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码