理解FPGA中的压稳态及计算压稳态的方法

压稳态什么时候会导致设计失败?

如果数据输出信号在寄存器下次采集数据之前,转换到有效状态,那么,压稳态信号不会对系统工作有不利影响。但是,如果压稳态信号不能在它到达下一设计寄存器之前转换到低电平或者高电平状态,那就会导致系统失败。继续山和球的形象解释,当球到达山脚( 稳定逻辑状态0 或者1) 的时间超出分配的时间后,即,寄存器tCO 加上寄存器通路所有时序余量的时间,就会出现失败。当压稳态信号没有在分配的时间内稳定下来时,如果目的逻辑观察到不一致的逻辑状态,即,不同的目的寄存器采集到不同的压稳态信号值,出现逻辑失败。

同步寄存器

当信号在不相关或者异步时钟域电路之间传送时,在使用该信号之前,需要将信号同步到新的时钟域。新钟域中第一个寄存器起到了同步寄存器的作用。

为消除异步信号传送时压稳态导致的失败,电路设计人员通常在目的时钟域中使用多个串联寄存器( 同步寄存器链或者同步器),将信号重新同步到新时钟域上。采用这些寄存器,在设计中的其他部分使用压稳态信号之前,该信号能够有更多的时间转换到确定状态。同步寄存器至寄存器通路上的时序余量是压稳态信号稳定所需要的时间,被称为压稳态稳定时间。

同步寄存器链或者同步器是满足以下要求的寄存器序列:

■ 链上的寄存器都由相同的或者相位相关的时钟进行同步

■ 链上的第一个寄存器由不相关的时钟域进行驱动,即异步驱动。

■ 每个寄存器只扇出连接一个寄存器,链上的最后一个寄存器除外。

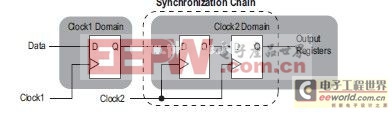

同步寄存器链的长度是满足以上要求的同步时钟域中的寄存器数量。图3 是长度为2 的同步链的例子,假设输出信号被送入多个目的寄存器。

图 3. 同步寄存器链实例

注意,异步输入信号,或者在不相关时钟域之间传输的信号,会在相对于采集寄存器时钟沿的任意点进行转换。因此,设计人员无法预测数据转换前的信号转换顺序或者目的时钟边沿数量。例如,如果在时钟域之间传送异步总线信号,并进行同步,数据信号会在不同的时钟沿进行转换。结果,会接收到不正确的总线数据。

设计人员必须适应这种电路工作方式,例如,双时钟 FIFO (DCFIFO) 逻辑存储信号或者握手逻辑等。FIFO逻辑使用同步器在两个时钟域之间传送控制信号,然后,数据被写入双端口存储器,或者读出。Altera 为这一操作提供DCFIFO 宏功能,它包括各种级别的延时,为控制信号提供亚稳态保护。如果异步信号被用作两个时钟域之间的部分握手逻辑,控制信号会指出数据什么时候才能在时钟域之间进行传输。在这种情况下,采用同步寄存器以确保亚稳态不会影响控制信号的接收,在任何亚稳态条件下,数据都有足够的建立时间,在使用数据之前达到稳定。在设计比较好的系统中,每一信号在被使用之前都能达到稳定状态,设计可以正常工作。

计算亚稳态MTBF

亚稳态平均故障间隔时间MTBF 大致估算了亚稳态导致出现两次设计失败之间的平均时间。较大的MTBF( 例如亚稳态失败间隔数百甚至数千年) 表明非常可靠的设计。所需要的MTBF 取决于系统应用。例如,急救医疗设备需要的MTBF 要比消费类视频显示设备长得多。增大亚稳态MTBF 能够减小信号传输导致设备出现亚稳态问题的概率。

可以使用设计信息以及器件特征参数来计算设计中某些信号传输或者所有信息传输的亚稳态MTBF。采用下面的公式和参数来计算同步器链的MTBF:

![]()

C1 和C2 常数取决于器件工艺和工作条件。

在fCLK 和fDATA 参数取决于设计规范: fCLK 是接收异步信号时钟域的时钟频率, fDATA 是异步输入数据信号的触发频率。较快的时钟频率以及触发数据能够降低( 或者劣化) MTBF。

tMET 参数是亚稳态信号达到确切状态的亚稳态建立时间,即,超出寄存器tCO 的时序余量。同步链的 tMET 是链上每一寄存器输出时序余量之和。

设计中每一同步器链的MTBF 确定了总的设计MTBF。同步器的失效率是1/MTBF,将每一同步器链的失败概率相加得到整个设计的失败概率,如下所示:

![]()

设计亚稳态MTBF 为1/failure_ratedesign。

设计人员使用Altera® FPGA 时,不需要手动完成这些计算,这是因为Altera Quartus® II 软件将亚稳态参数集成到了工具中。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码