一种用于光盘伺服控制系统的通用滤波器的设计

需要特别说明的是,在对MEM1和MEM2存放数据时,滤波器系数和X(k)、Y(k)必须是一一对应的,从而使每次读数据时的读地址相同,简化寻址单元的设计。滤波器的运作是由状态机(逻辑单元)控制的,流程如下:

(1)初始化系数存储单元,根据SP算出X(k)、Y(k)在MEM2中的分界地址SP+N和SP+M+N;

(2)从MEM1、MEM2的(SP+j)单元读出数据送MAC计算,MEM2读出的数据写回(SP+j-1)单元,j为0时的数据无效,不写回;当j为M+N时,转步骤(4);

(3)j加1,重复步骤(2);

(4)一次Y(k)计算完成。将当前ADC的输入写回到MEM2的(SP+M+N)单元;

(5)将本次计算所得的Y(k)送SP+M,j复位为0,重复步骤(2)。

3 实现与仿真

按照上述设计思想,用Verilog对系统进行RTL描述,代码层次结构如图4所示,其中,F―TOP为顶层wrapper模块,连接MAC、STATEM、SRAM三个子模块。MAC实现图3中虚线所示的Booth乘加器,得到的乘积为32 bits数,然后经过舍入调整(rounding)将其转化为16 bits数;STATEM模块实现上文提到的控制流程;SRAM模块由系数SRAM和数据SRAM(存放X(k)、Y(k))组成,分别对应图3的MEM1、MEM2,为了方便后面的验证,直接调用Xilinx的SRAM单元RAMB4―S8―S8。

代码使用synopsys VCS进行仿真,通过debussy的PLI接口生成fsdb波形文件。在debussy中对波形(图5所示是波形仿真图)进行分析。当前的配置寄存器的值为0x0000018f,为三阶IIR滤波器。READ―EN为读使能信号,低电平有效。STATE―WE―LOC为写使能信号,低电平有效。RADDR―LOC和WADDR―LOC是存储单元的地址,地址范围从0到5,与三阶IIR滤波器对应;当WADDR―LOC为5时,写入的是X(k),下一时钟周期变为2,写入Y(k)(标尺线所对的值0x000a,已经过rounding处理)。XIN―LOC和YIN―LOC是MAC的输入数据。STATE―LOC和YIN―LOC是MAC的输入数据。CUR―STATE为状态机的状态变化,可以看出,与前面的状态含义和状态机实现策略一致。这里,读写地址在整个运算过程中都占用两个时钟周期是为了保证MAC运算的正确完成,当X(k)和计算所得的Y(k)写回时,不涉及MAC运算,因此,只分配一个时钟周期。

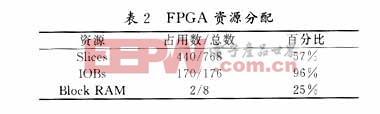

为了确保滤波器以及整个控制系统设计的正确性,我们选用Xilinx Spartan2的XC2S50系列做FPGA验证。首先,在synplify中生成网表文件(edf),然后,通过Xilinx ISE生成带延时信息的单元网表文件(v)和线延时文件(sdf),用于在VCS中进行后仿真,最后生成FPGA下载文件(bit)。XC2S50硬件占用情况如表2所示。表2所示是FPGA资源分配表。

该滤波器在光盘伺服控制电路中的应用表明,激 光头的恢复时间、稳态误差等计数参数均满足实际要求。该单元可直接用于伺服芯片的聚焦寻迹模块。

4 结束语

文中介绍了一种通用可配置滤波器的设计和实现。通过对该滤波器的配置可实现不同阶数和类型的滤波器,从而加大以数字滤波为基础的伺服控制系统应用的灵活性。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码