基于DDS技术的多路同步信号源的设计

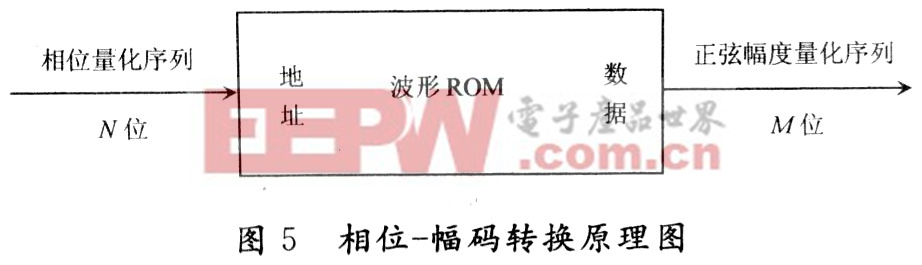

用相位累加器输出的数据作为波形存储器的取样地址,进行波形的相位一幅码转换,即可在给定的时间上确定输出的波形的抽样幅码。本设计利用FPGA资源,构造一个10位的ROM进行数据的存储和转换。

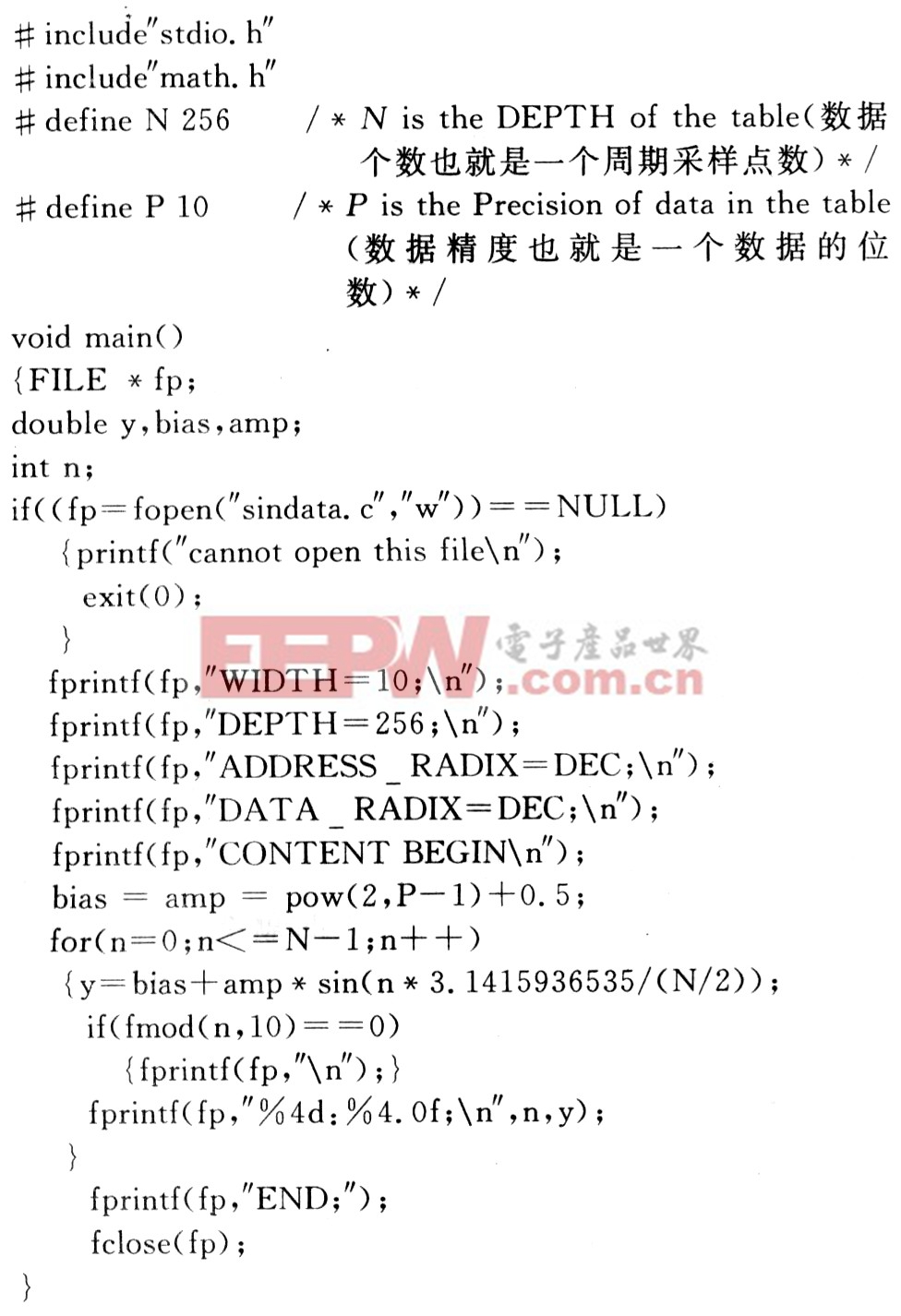

ROM可利用Quartus的插件管理程序Megawiz-ard plug-in manager容易获得,这里给出正弦波形数据生成的C程序,来生成ROM存储的数据。要想生成其他波形的数据,只需要简单修改其中的波形表达式即可。

3 仿真与调试

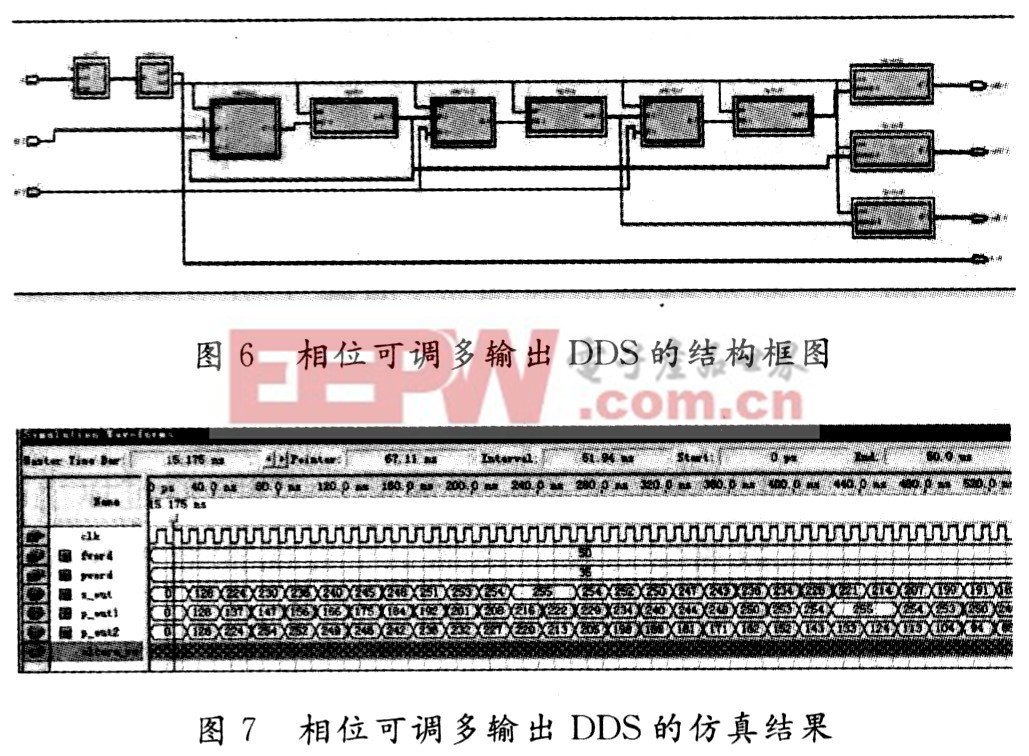

本设计在Quartus Ⅱ中进行分析和综合后,得到该相位可调多输出DDS的结构如图6所示。

在Quartus Ⅱ中,输入控制信号:Fo=100 MHz,fword=50,pword=35,进行仿真,其仿真结果如图7所示。在Quartus中生成的仿真数据经过验证完全正确,得到了同频和可调相的三个正弦波的幅值数据序列,完全满足设计要求。

4 结 语

本设计运用VHDL硬件编程语言和DDS技术,结合FPGA高速器件,实现了多路信号的同步输出,很好地解决了要求信号之间同频率可调,相位连续可调的问题,且具有易于程控、相位连续、输出频率稳定度高、分辨率高等优点,并且采用一个FPGA块就解决了传统上需要三个DDS才能解决的问题,也大大降低了设计成本。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码