基于DDS技术的多路同步信号源的设计

单片机及总线配置电路通过键盘实现人机接口。通过4×4矩阵式键盘可以将频率选择、初始相位选择等数据输入单片机并经单片机处理后送FPGA,实现DDS的调整。

FPGA是完成DDS多信号产生的核心部件,完成DDS多路同步信号的产生。

2 基于DDS技术的多路同步信号输出的FPGA核心设计

2.1 一般DDS的工作原理

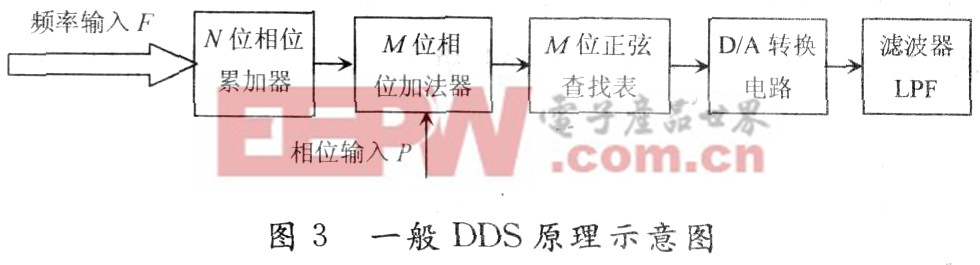

DDS(Direct Digital Synthesizer)是从相位概念出发直接合成所需的波形的一种频率合成技术。一个DDS信号发生器是由:相位累加器、波形数ROM表、D/A转换器以及模拟低通滤波器LPF组成,原理框图如图3所示。DDS技术的核心是相位累加器,相位累加器在稳定时钟信号的控制下产生读取数据的地址值,随后通过查表变换,地址值被转化为信号波形的数字幅度序列,再由数/模变换器(D/A)将代表波形幅度的数字序列转化为模拟电压,最后经由低通滤波器将D/A输出的阶梯状波形平滑为所需的连续波形。相位累加器在时钟Fc的控制下以步长F作累加,输出的值与相位控制字P相加后形成查表的地址值,对波形ROM进行寻址。波形ROM的输出值即是幅度值,经过D/A变换后形成阶梯状的波形,最后通过低通滤波平滑成所需的波形。合成信号的波形取决于ROM表中的幅度序列,通过修改数据可以产生任意波形,如果要产生多种波形,只需把所需的多种波形数据存放到波形ROM表中。一般DDS的原理示意图如图3所示。

2.2 同步多路输出DDS的工作原理

同步多路输出DDS工作原理示意图如图4所示。

由方框图可以看出,从同一个相位累加器输出的地址值在进行查表之前,根据需要有不同的相位字进行加法运算,再根据新的地址进行查表,从而形成波形之间需要的相位值。由于各个输出信号是在DDS内对同一个累加器输出的地址进行相位的加法,参数一致,相位的可调性非常好。频率取自同一频率字,各个信号存在固定的同步同频特性,因此输出的信号源同步性能优越,完全满足设计要求。

2.3 相位累加器的设计

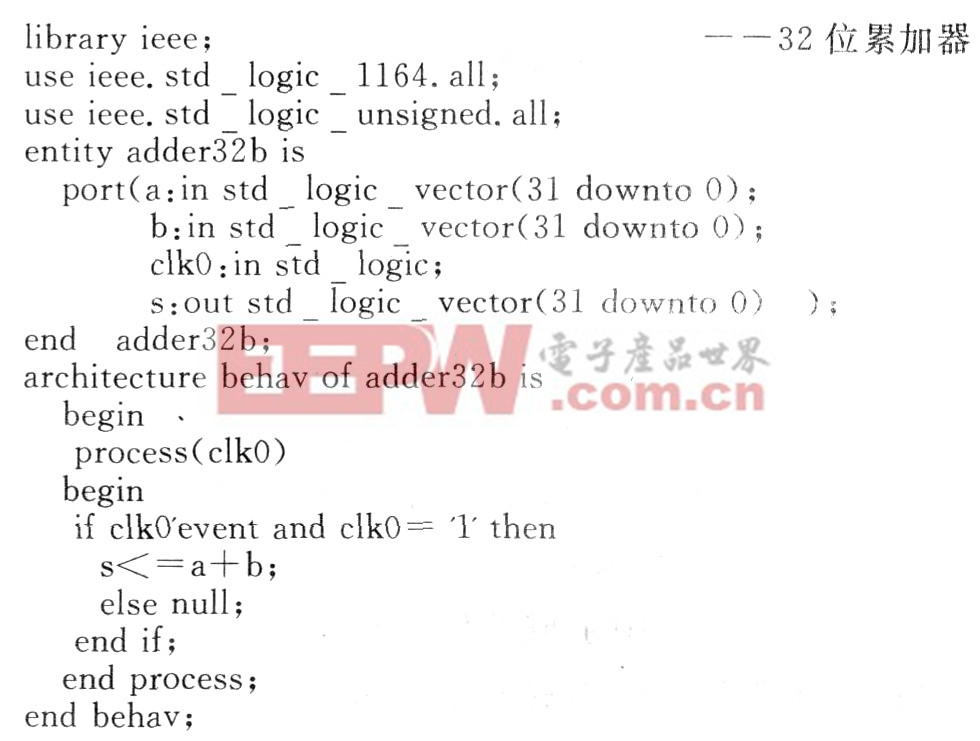

相位累加器是DDS设计的核心部件。本设计相位累加器由32位加法器与32位寄存器级联构成。累加器将加法器在上一个时钟作用后所产生的相位数据反馈到加法器的输入端;使加法器在下一个时钟作用下继续与频率控制字(K)进行相加,实现相位累加,当相位累加器累加结果等于或大于232时就会产生一次溢出,回到初始状态,完成一个周期性的波形输出。本设计累加器用VHDL语言[quartus6.0]设计实现如下:

32位累加器模块实现:

2.4 波形存储器的设计

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码