雷达视频信号模拟器的硬件设计与实现

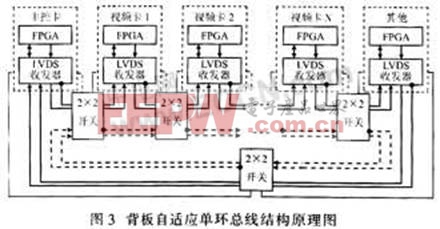

该系统需产生和差三通道I,Q共6路回波信号,而每路信号都需将对应的杂波、噪声及目标参数下载到Flash存储器中。由于数据量较大,且考虑到下载速度,该背板总线采用了自行设计的单环总线结构。该结构采用基于低压差分信号收发器DS92LV18和低压差分信号传输模拟交叉点开关SCAN90 CP02来实现。通过各子卡的插拔,实现对SCAN90 CP02的逻辑控制,从而保证无论背板各扩展槽是否有卡,整个环路都保持封闭状态。DS92LV18的主要性能:15~66 MHz,18:1/1:18串行/解串器;收发一体设计;内置发射/接收数字锁相环;提供帧同步、帧检测、时钟恢复功能;可进行单器件环路测试,器件引脚基本兼容,设有本地及线路环回模式。SCAN90CP02的特点:每通道的传输速率达1.5 Gb/s;低功耗;在双中继器模式下,最高速率时,电流为70 mA;低输出抖动;配置有预增强功能,可驱动有损耗的背板和电缆LVDS/BLVDS/CML/LVPECL输入;LVDS输出。由这两款器件组成的环网总线最大数据乔吐速度为1.188 Gb/s,能够满足快速下载数据的要求。图3给出单环总线的结构原理框图。

2.3视频信号卡

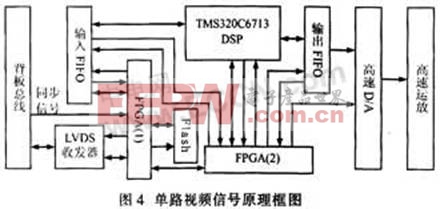

视频信号卡为整个系统的核心部分,因其视频信号的生成所涉及的运算量很大,单个DSP难以生成多路视频信号,同时出于系统升级的考虑,因此该视频信号模拟器的每路都使用高性能的TMS320C6713型浮点数字信号处理器。该DSP采用先进的超长指令字结构,内置8个独立的功能单元、2个定点算术逻辑单元,2个浮点乘法器,4个浮点ALU、32个32位通用目的寄存器,4 K字节的L1高速程序缓存区,4 K字节的L1高速数据缓存器,256 K字节的L2两级数据缓存器。这种结构能最大限度地发挥8个功能单元的并行计算能力,使得300 MHz系统时钟工作下的DSP性能达到2400MI/s和1 800MFLO/s。

单路视频信号生成原理框图如图4所示。其中,DSP完成视频信号运算;FPGA(1)用于控制LVDS收发器接收来自总线上的命令、地址及数据,在产生视频信号前,将上位机事先产生的杂波数据、噪声及目标参数下载至Flash存储器中。在生成视频信号期间,FPGA(1)判断DSP的工作状态,将Flash存储器的数据读入输入FIFO中;FPGA(2)主要完成DSP渎写输入、输出FIFO的逻辑转换,接收来自DSP计算视频信号相对PRF信号的延迟时间,通过FPGA(1)接收同步信号,读取输出FIFO的数据并启动D/A转换器;DSP将输入FIFO的数据渎人其内部RAM,根据对应的数据及目标参数生成所需的视频信号数据,并将运算后的数据写入输出FIFO。FIFO采用IDT72V17160,其读写速度可达100 MHz。

3系统工作流程

上位机根据噪声和杂波模型脱机产生和路、方位差、俯仰差三通道I/O杂波、噪声及目标参数,由上位机发出指令、卡地址将各通道的数据下载至对应的Flash存储器。然后,由上位机生成DSP指令,发送至主控卡的缓存中,触发同步信号,将指令发送至DSP,同时视频卡根据该同步信号产生视频信号,DSP对视频信号进行采样、运算,并将其结果及状态信息发送至上位机显示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码