2009年晶圆级封装趋势

更小的引脚节距

在过去的几年中,引脚节距从0.5mm演变成0.4mm,现在的目标是0.3mm。“产业何时能发展到那里,很大程度上取决于基板何时能发展到那里。还没有人向我们要求0.3mm引脚节距的产品,但是我们一直被询问对它的工程评估。”Hunt指出,实现0.3mm的困难包括很难找到匹配的基板。“另一个问题是可靠性。每次引脚节距改变时,焊球尺寸也会随之缩减。很明显,你不能在窄引脚节距上继续使用大尺寸的UBM。但如果你缩小了UBM和焊球的尺寸,那么焊柱的支撑截面积也将降低;随之结构完整性下降,并将影响跌落测试的结果。”

然而,引脚节距从0.5mm转变为0.4mm时,ASE在温度循环性能上取得了进步,因为相同I/O数目下封装尺寸缩小了。对于更窄的引脚节距来说,封装尺寸不需要很大,因此到中性点的距离也下降了。Hunt说,这将导致节距收缩时温度循环性能的提升,但是跌落测试性能却有下降。因为主要用于便携式终端设备,所以跌落测试性能比温度循环性能更重要。人们经常会不小心跌落设备但却不经常把它们从-40°C的环境带到150°C的环境。

车载器件

在便携式WLP设备中,过去的要求是低功率但不要求大电流容量。“溅射薄膜足够好而无需进行电镀,”Hunt这样解释。“对于大电流的汽车应用和高精度的精密仪器,我们已经从溅射RDL和凸块下金属层(UBM)转为采用电镀,这样才能处理增加的功率和精密仪器所需的低电阻。”

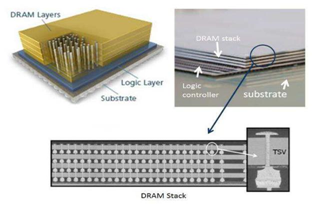

TSV用于增加封装密度

在市场上出现的某些高密度应用中,ASE看到了对TSV的需求。“我们已经为晶圆级芯片尺寸封装(WLCSP)做了一些TSV样品,使我们能在WLCSP中进行封装上封装(PoP),把另外一块芯片或者WLP组装到WLP之上,”Hunt说。“我们的样品显示出该方案的可行性,但问题是:以目前的技术条件,在经济上这是否可行?这个问题仍在探索中。”

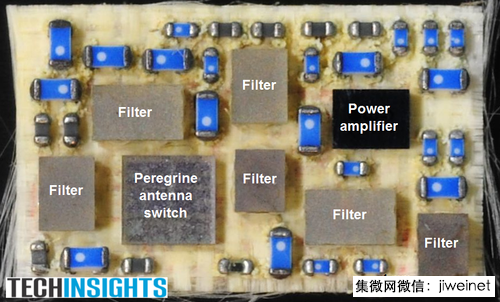

ASE自有在200mm晶圆上制作TSV的技术,但仍在工程研发阶段,尚未试图进行大规模生产。Hunt强调,它很可能会使成本增加,所以问题变成:折衷是否值得?“我们正在关注的另外一个趋势是将无源器件集成到WLCSP中,”他补充道。“这些器件将会进入再分布层,包括电感、不平衡变压器、匹配变压器,甚至是电容或电阻以提高设备功能。”

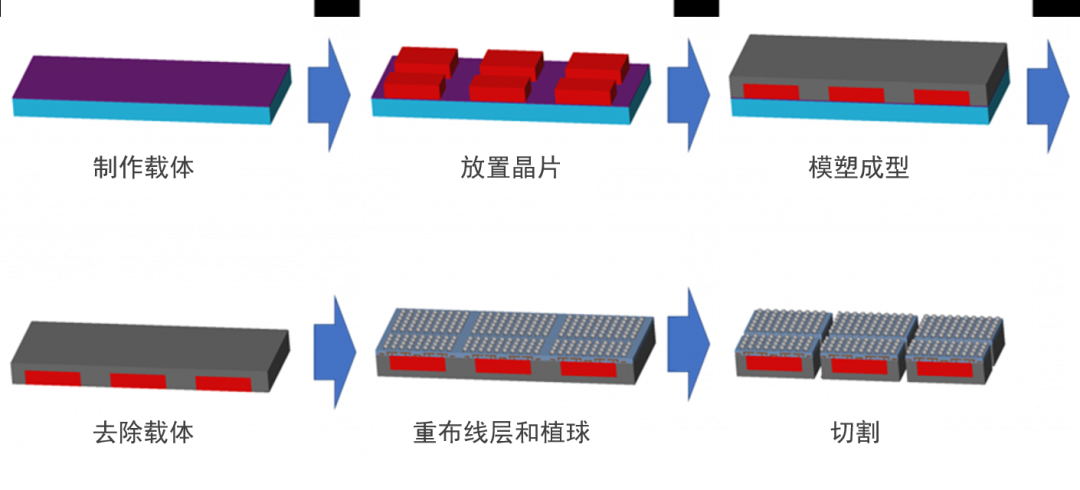

扇出

ASE从英飞凌得到扇出技术的授权。扇出是WLCSP技术的扩展,目前正处于验证阶段。ASE使用晶圆级工艺——但不是初始硅晶圆。“将晶圆上测试后已知性能良好的芯片切割下来,重新组装到辅助晶圆上,然后按照与硅晶圆相同的方法处理辅助晶圆,”Hunt解释道。“这将在初始硅芯片的限制范围之外创造出区域以放置焊料球。这意味着当你发展至65、45、32nm的技术节点时,你能够缩小硅的尺寸。你能够缩小芯片,将部分焊料球置于塑封材料之上,部分置于硅上。我们正为英飞凌验证该技术,希望能够在2009年以aWLP的商

标供应市场。它将扩展现有的WLP技术的能力,使之与倒装芯片芯片尺寸封装领域发生重叠。”

嵌入式闪存

另外一个趋势是用户正将闪存嵌入他们的设备。“对嵌入式闪存的要求是只能进行低温工艺,”Hunt说。“现今用于再分布和再钝化的聚合物——尤其是聚酰亚胺和苯并二唑类聚合物(PBO)——需要的温度是325-375°C。闪存理想温度要求低于200°C。”这需要引入在可靠性方面不亚于现存聚合物的新型低温固化聚合物。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

相关文章

-

-

-

-

-

-

2016-06-28

-

-