Aurora协议的高速传输系统的研究与FPGA实现

编者按:随着5G技术的发展,对信号的带宽以及传输速率都有较高的要求,同时对高速率数据解析处理和传输使得对信号的测试难度变得越来越有挑战性,目前Aurora协议作为最常用的一种高速传输协议,被广泛应用。本研究主要基于Xilinx公司的ku060系列芯片,使用FPGA内部自带的Aurora协议的IP核进行设计实现,为了满足Aurora协议的数据传输,本设计使用了数据转换模块,对传输过来的数据进 行处理,以达到Aurora协议数据传输的要求。

基金项目:电子测量仪器技术蚌埠市技术创新中心:高性能5G增强移动宽带通信矢量信号发生器(AHZQ3026)

随着5G 技术的不断发展,新一代的通信技术也迎来了发展的高潮。此外,随着智能设备的普及,对数据流量也带来了较大的激增。5G 技术的发展对数据传输的实时性要求很苛刻。新一代的通信技术存在大量的研究难题,除了大带宽、高速率以及sub6G 数据分析之外,还有微波和毫米波信号分析。5G 技术最大的挑战就是随着5G 高速率数据传输会导致信号带宽以及基带处理速度都将大幅度的提升,因此对高速的数据实时处理分析就变得越来越有难度[1]。

Xilinx 公司的FPGA 内部镶嵌了Rocket IO高速串行收发器,从而能够简化光口传输的硬件电路。Aurora 协议是Xilinx 公司对外免费开放的一个高速光口传输协议,不仅方便了设计者自行添加上层应用,而且能够适配大多数嵌有Rocket IO 高速串行收发器的FPGA。FPGA内部携带的IP 核可以提供用户接口方便与FIFO 接口对接,其他的传输协议需要设计者自行设计GTP 接口的逻辑,端口的逻辑设计复杂;与此同时,Aurora IP 核在初始化时形成的Aurora 传输通道能够满足任何大小的数据帧,并且当传输通道被随意打断时,打断空缺的地方能够自动进行填充,从而达到满足传输过来的不连续信号的要求。本文利用FPGA 自带的Aurora 协议进行高速光口传输协议设计与实现,并对此方案进行测试。

1 系统架构

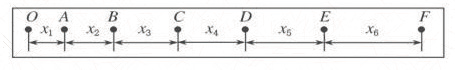

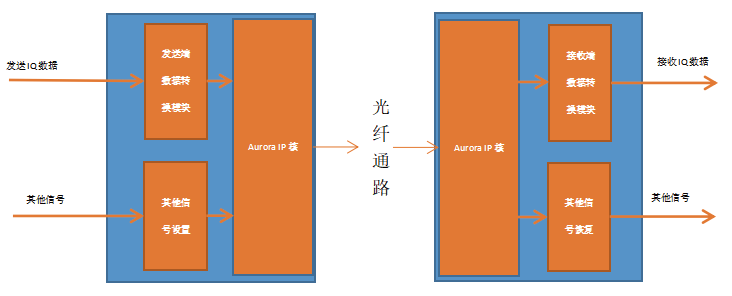

基于Aurora 协议的高速传输系统的结构图如图1所示,该系统主要是实现射频单元与基带处理单元之间的Aurora 协议的数据传输链路。结构图中Aurora 传输协议是通过Xilinx 公司的FPGA 自带的IP 核实现的,为了能够满足Aurora 协议传输的数据要求,设计了数据转换模块,此模块主要作用是传输速率的匹配。在信号的发射端将采集的IQ 数据通过数据转换模块将数据转换成满足Aurora 协议传输的帧结构和速率;在接收端通过数据转换模块将Aurora 协议传输过来的数据恢复成规定的采样速率的连续IQ 数据。

图1 系统结构

2 Aurora协议

2.1 Aurora协议简介

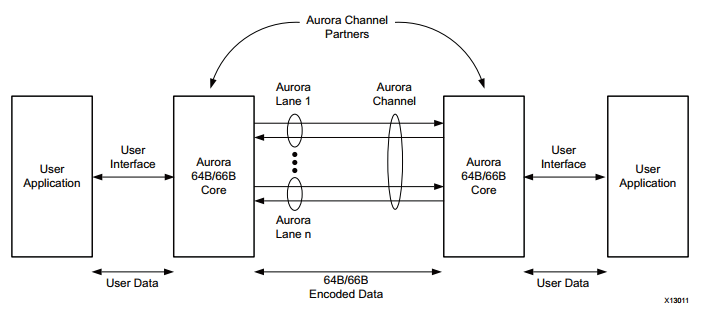

Xilinx 公司为了实现高速传输开发了Aurora 协议,它是一种可裁剪的轻量级链路层协议,实现方式是通过在相应的器件内部制定相应的IP 核。在物理层方面,它提供了透明的接口,将Rocket IO 硬核封装到了协议的内部,通过Rocket 的并行绑定,从而能够实现数据传输带宽的完美升级。与此同时,Rocket IO 硬核不仅能进行上层自定义,还能被工业标准协议采用。Aurora协议运用的是有线连接的通信模式,协议中不仅仅是将物理层接口和数据格式都定义好了,还将时钟校准、初始化等内容也进行了相应的定义。Aurora 协议传输方式包括流和帧两种,能满足不同用户的使用。Aurora 协议传输结构图如图2 所示。

图2 Aurora协议传输结构

Aurora 协议内部有多种不同的编码方式,其中8B/10B 和64B/66B 两种编码方式最为常用。本文设计主要采用的是64B/66B 编码方式。FPGA 内部自带的Aurora IP 核模块主要功能有:①通道的传输逻辑,主要是负责模块的初始化、GTX 和GTH 收发器的驱动、错误检测以及处理控制字符的编解码;②提供用户接收接口,将通道传输过来的数据送到用户程序中,从而执行控制能力;③提供用户发射接口,将用户程序发送过来的数据传输到通道中,从而执行发送功能。

本设计Aurora 数据传输方式选择的为流模式接口设计。该模式接口主要包括复位接口、接收数据信号接口、发送数据信号接口、接收数据信号使能接口、发送数据信号使能接口以及数据准备接口。

2.2 Aurora协议数据传输流程

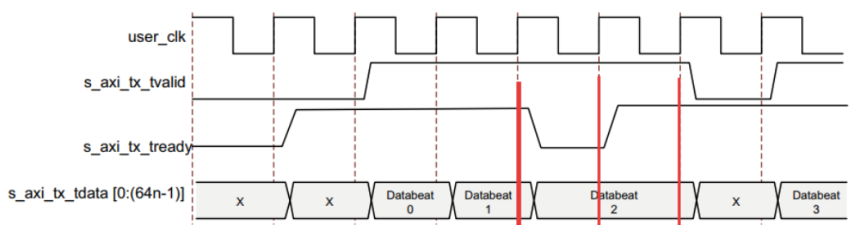

Aurora 协议数据传输方式选择为Streaming 模式,在该模式中,Aurora64B/66B 通道采用流水线方式处理。此时接口的数据会传输到发射数据接口s_ax_tx_tdata端口,在发送数据有效位s_ax_tx_tvalid 无效时,除了数据传输的时钟外,缓存的word 之间会产生间隙。当传输数据到达接口的接收端时,需要将数据立刻读取,否则会造成数据丢失。

图3 为发送数据传输逻辑图,从图中可以看出在第1 个周期时s_axi_tx_tvalid 和s_axi_tx_tready 均为0,此时表示Aurora IP 核和用户逻辑数据传输均没有准备好;等到第2 个周期时s_axi_tx_tvalid=0 和s_axi_tx_tready=1,表示Aurora IP 核已经做好了传输数据的准备,等待用户逻辑传输数据;等到第3 个周期时s_axi_tx_tvalid=1 和s_axi_tx_tready=1,表示用户逻辑传输数据,并且会将需要传输的数据放到了s_axi_tx_tdata总线上,此时数据会从用户逻辑端传输到Aurora IP 核端;在位置1 的周期内,s_axi_tx_tready 信号被拉低,此时的数据是无效的,在位置2 的周期内s_axi_tx_tready 信号又被拉高,此时的数据是有效的;在位置1 的周期内,s_axi_tx_tready 信号被拉低,此时的数据是无效的;在位置3 的周期内s_axi_tx_tready=1 和s_axi_tx_tvalid=0,此时无数据传输。

图3 Aurora协议发送数据传输逻辑图

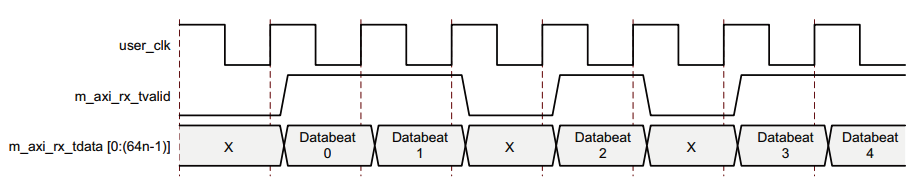

图4 为接收数据传输逻辑图,从图中可以看出在接收数据时,只要m_axi_rx_tvalid 信号有效时,就开始接收数据,当m_axi_rx_tvalid 信号无效时,不接收信号。

图4 Aurora协议接收数据传输逻辑图

3 数据转换设计

为了满足5G 数据传输中30 kHz 和60 kHz 两种载波间隔的基带数据传输,在接收端和发射端采用了两种采样率即122.88 MHz 和245.76 MHz,但是AuroraIP 核使用的是245.76 MHz 固定的频率进行数据的读入与输出。因此在对于122.88 MHz 采样率的数据输入就需要将两个帧的数据进行缓存,然后通过一个245.76MHz 的帧时间读出,随之输出一个无效的帧数据,等待下一帧数据的到来。接收端与之一样,等到2 个122.88 MHz 的有效数据缓存之后再用245.76 MHz 的频率输出。

4 Aurora协议的FPGA实现及验证

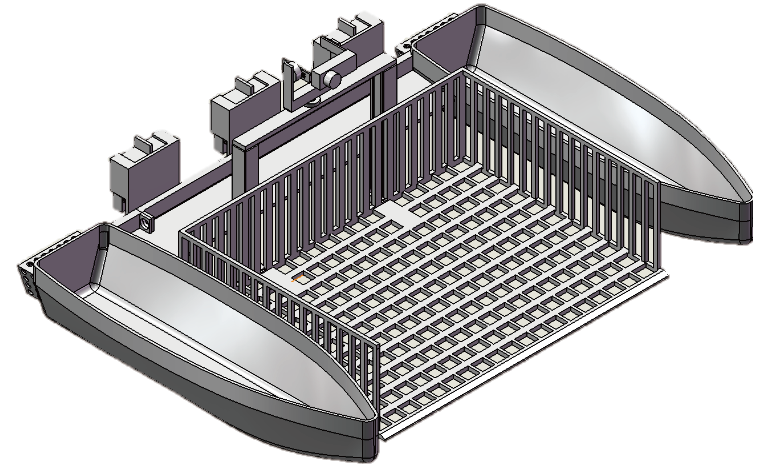

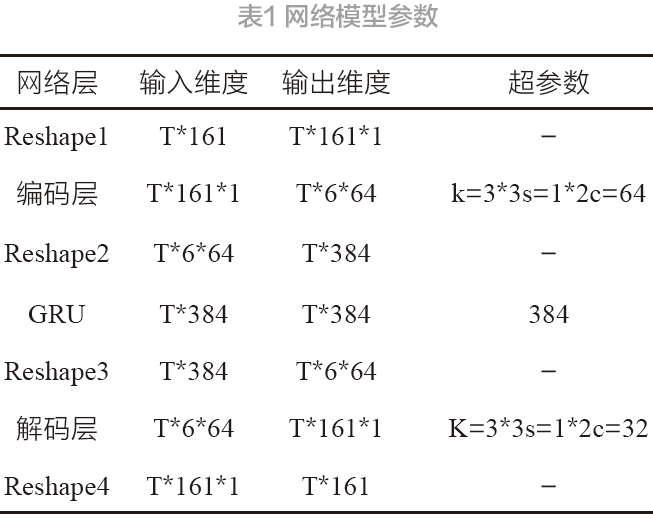

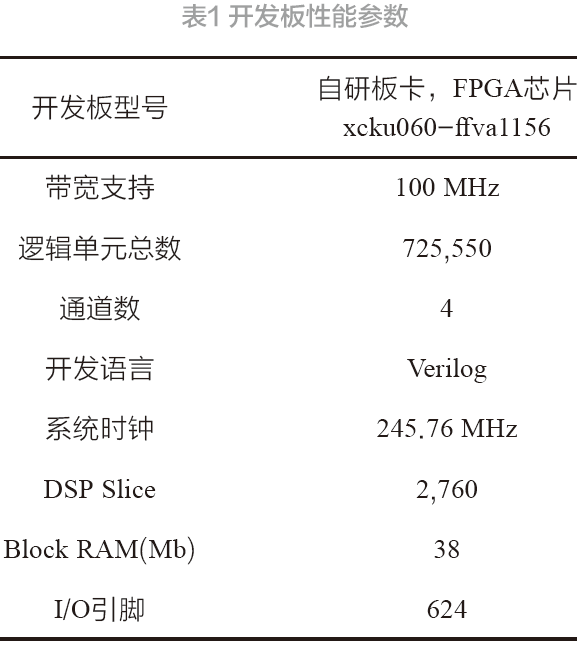

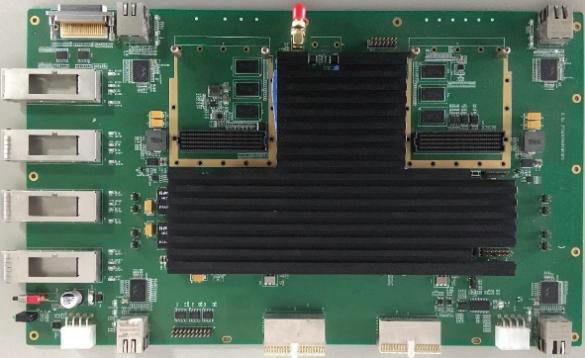

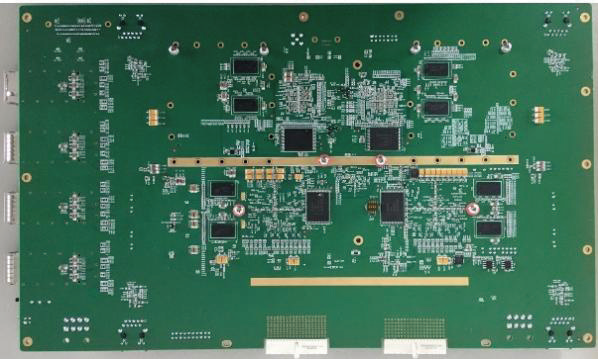

本研究将对Aurora 协议高速传输功能通过FPGA进行实现,并且通过硬件平台来进行功能验证。图5 是FPGA 硬件开发板,首先介绍一下开发板的性能参数以及它的开发能力,开发板参数如表1 所示,开发板的硬件结构图如图5 所示。

图5 FPGA开发板正反面

4.1 顶层模块设计

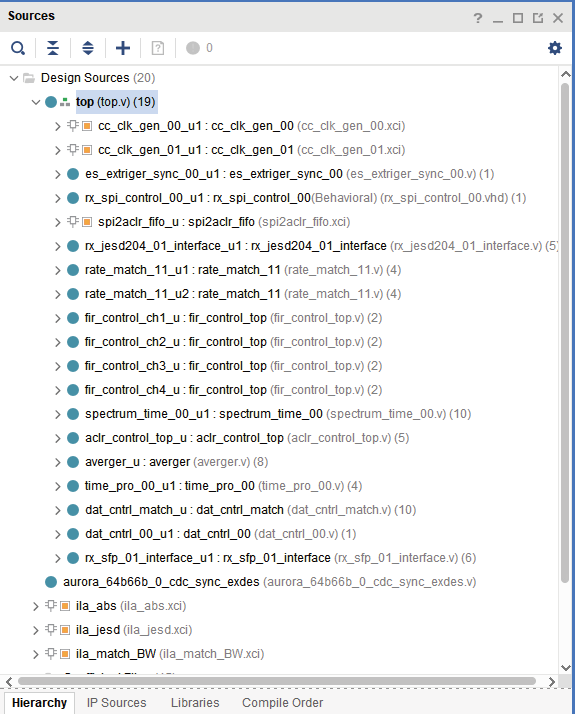

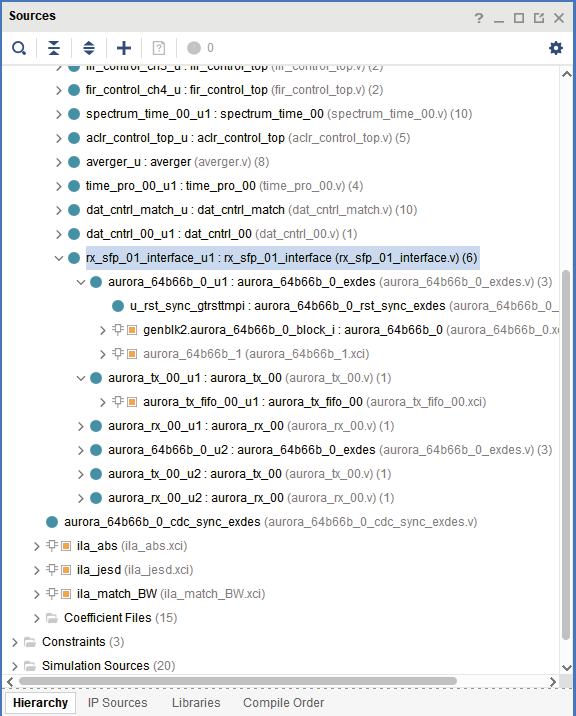

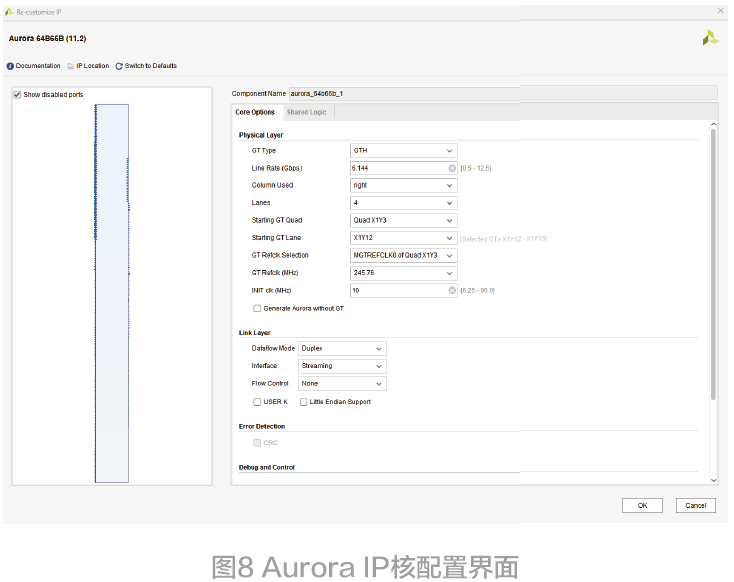

图6和图7给出了设计的顶层核Aurora 协议模块的结构,Aurora IP 核设置如图8 所示。

图6 程序整体模块

图7 Aurora协议模块

top:设计的顶层文件;

rx_jesd204_01_interface_u1:采集模块,将采集到的射频信号转换成245.76 MHz 的时钟速率;

rx_sfp_01_interface_u1:Aurora 协议实现的顶层模块。

4.2 测试验证

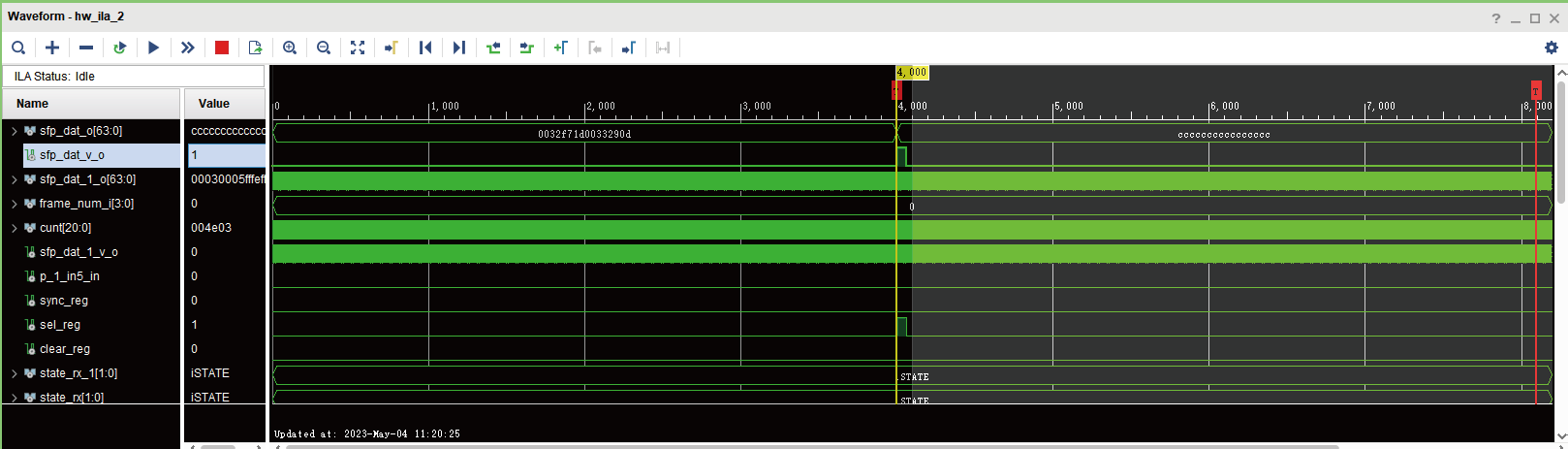

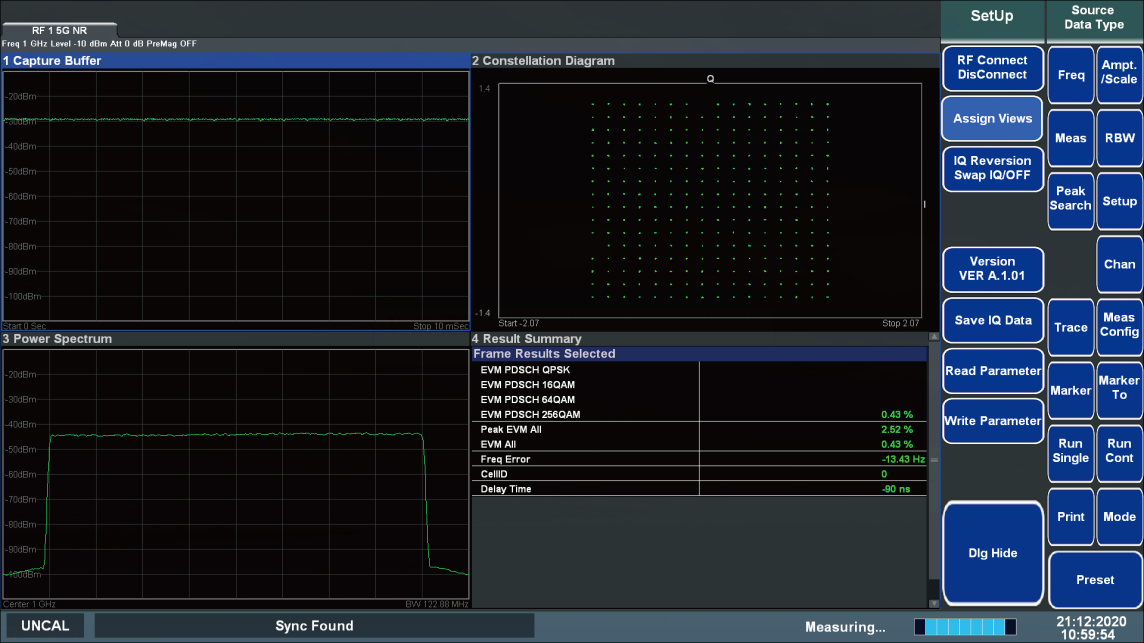

本设计采用Vivado2018.3 软件进行代码编写、编译及上板验证,该开发软件内部集成了大量的RAM、乘法器以及FIFO 等常用的IP 核,从而能够大大降低了功能的开发难度。数据速率转换模块是将外部的异步速率的信号转换成Aurora 核数据时钟的信号。采用Xilinx ku060开发板进行功能仿真验证,使用的FPGA芯片型号为xcku060-ff va1156。通过ILA 监测器来观察Aurora协议信号传输功能是否正常。最后通过DSP 识别CCCC_CCCC 数据头将IQ 数据传输给算法库进行解调,软件将解调结果显示出来。测试结果如图9 和图10 所示。

图9 FPGA捕捉到CCCC_CCCC数据头

图10 IQ数据解调结果

5 结束语

本研究主要完成了Aurora 协议高速传输系统研究和FPGA 实现验证。为了实现射频RF 单元和基带BU单元之间的Aurora 协议的数据链路,需要将发送和接收的数据格式匹配到Aurora 协议的数据格式。数据传输的速率匹配难点主要在于高速处理硬件的实现。为了匹配不同采样率的数据Aurora 传输,设计了数据转换模块。经过在Xilinx ku060 开发板测试,验证了Aurora协议高速数据传输的正确性,确定了本实现方案的可行性。

参考文献:

[1] 周代卫,王正也,周宇,等. 5G终端业务发展趋势及技术挑战[J].电信网技术, 2015,3:64-79.

[2] 焦志超. 一种基于Aurora协议的多通道数据传输系统设计[J].电子世界,2021,620(14):188-189.

[3] 袁行猛, 徐兰天.基于FPGA的高速光纤通信基带板的设计[J].电子产品世界,2018,25(7):8-61.

[4] 李维明, 陈建军, 陈星锜. 基于Aurora协议的高速通信技术的研究[J].电子技术应用,2013,39(12):37-40.

[5] 祁永鑫. 基于Aurora协议的多通道高速可配置数据采集系统设计[D].荆州:长江大学,2022.

(本文来源于威廉希尔 官网app 杂志2023年6月期)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码