使用LabVIEW FPGA模块设计IP核

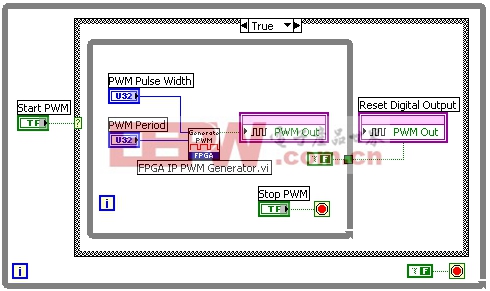

图8:展示PWM发生器IP的使用方法的VI范例

总结

如果创建的IP代码模块灵活且易于使用,那么LabVIEW FPGA IP代码模块可以在应用开发中提供显著的优势和节约。该文档所介绍的指导方针将有助于确保IP可以方便地复用并无须为单个应用进行定制处理。

下面是在开发任何LabVIEW FPGA IP过程中应当遵循的指导方针的总结列表:

I/O资源不应嵌入在IP代码模块的框图中。

请勿在IP中使用项目引用的存储器读写函数或FIFO读写函数。如可能,使用一个VI scoped存储块或FIFO(LabVIEW 8.20)。

文档化表述IP中存储器(存储器拓展例程存储块、FIFO和查询表等)的所有使用。在IP的分布中包含任何存储器拓展例程存储块VI。

不要在IP中包含任何循环结构或等待/循环定时器函数,除非这便是该IP的主要目标。

在IP中使用局部变量存储状态信息。

文档化表述IP的任何非正常的定时行为。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码