基于FPGA的可键盘控制计数电路的设计与实现

2.1.2 键盘扫描电路工作原理

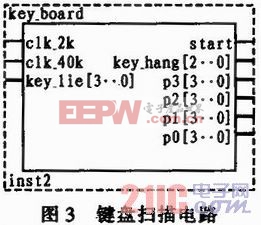

图3为键盘扫描原理图。CLK_40K为键盘扫描工作时钟,连续读取数据输入端KEY_LIE[3..0]的信息;CLK_2K为键值控制工作时钟信号,无键按下时控制电路循环扫描输出;P3,P2,P1,P0为键盘译码输出BCD码形式;START端为数据输出标志信号,当P3-P0输出时,START端输出一个脉冲。工作时,由行信号输出端KEY_HANG[2..0]循环输出“110”,“101”,“011”。当没有按键按下时,扫描电路列信号输入端检测到“1111”。当有按键按下时,例如按下1键,此时行信号KEY_HANG[2..0]输出“011”,由图2可知。列信号输入端将检测到“0111”,在扫描译码时,可根据行信号输出和列信号输入数据同时判断“0110111”对应数据为1。

2.1.3 键盘扫描电路VEIDL实现

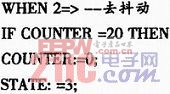

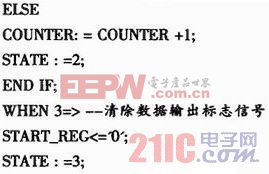

键盘扫描电路主要有判断按键有无按下,键值识别和去抖动处理等功能。其中去抖处理主要为了避免外界振动引起按键误动,以及保证按键每稳定闭合一次,系统仅对其响应一次。采用不同的键盘其机械抖动时间各异,本文设置去抖时间为20 ms。图4为键盘扫描电路VHDL描述流程图。以下是去抖动程序关键代码:

2.2 可预置数BCD码计数电路

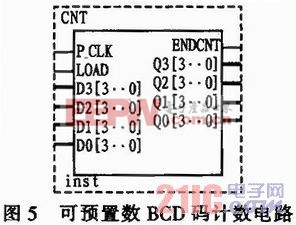

图5为可预置数BCD码计数电路。置数端LOAD为高电平时,将通过键盘设置的数并行置入到D3~D0。然后对输入的脉冲直接进行BCD码减法计数,由Q3~Q0输出。计数结束,ENDCNT端输出一个脉冲。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码