一种多路同步数据采集系统的设计

图5 CS5451A一帧数据输出图

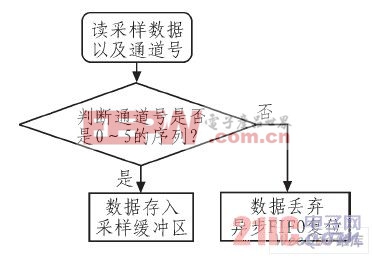

4 中断服务子程序的设计

CPU读采样数据是在中断服务子程序中设计的,在中断程序中读走采样值数据,并判断通道号是否对应。软件流程如图6所示。

图6 软件流程图

5 结论

本文利用CS5451A设计一个通用的多路数据采集系统,利用XILINX SPARTAN3E系列FPGA芯片实现异步FIFO和采样数据串并转换模块的设计,CPU不用直接用SPI控制器接收CS5451A芯片输出的串行格式的数据,只需要把ADC输出的串行数据通过串并转换模块存入FIFO缓冲区,并产生一个中断信号,在CPU的中断子程序中读出采样数据。该方案已经在低压继电保护装置中得到了应用,通过试验本系统的数据采集精度可以达到0.2级。调试中发现,在进行PCB设计时,要注意以下几点:

1)模拟部分电路(差分输入以及参考电源部分)和数字部分(XIN、FSO、SDO、SCLK信号)应完全分开在不同的区域里。

2)良好的去耦对抑制CS5451A产生的噪声很重要,去耦电容一般为0.1 μF,且放到电源输入引脚尽可能近的地方,以达到良好的去耦效果。

3)如果系统要求工作在-40~+85℃的温度范围内,要求采样精度达到0.2级,必须使用外部高精度的参考电源。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码