基于LZW算法的数据无损压缩硬件实现

2 LZW算法FPGA实现

2.1 算法实现硬件结构

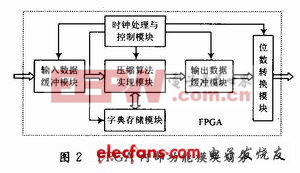

LZW数据压缩算法的FPGA硬件实现,其内部功能模块划分如图2所示。

2.2 各功能模块说明

输入/输出数据缓存模块完成FPGA所有数据传输工作,为了保证异步时钟域数据同步,使用FPGA片内的Block RAM构成一个FIFO对输入数据进行缓存。

字典存储器模块需要存放字典项的三部分内容:字典项编码、前缀码、当前码。将存储器的容量设计为1K。采用FPGA内部宏单元lpm-ram-dp(单口RAM)设计字典存储器。

算法实现模块要实现匹配串的查找、判断字典相应地址内容是否为空、比较字典地址相应内容是否匹配或冲突、冲突时重新生成地址、压缩编码输出控制、压缩结束控制等功能。

外接闪存数据宽度为8位,所以压缩后输出数据位数需要转换。数据转换模块就是实现压缩后数据由13位向8位的转换。

时钟处理与控制模块主要完成时钟的匹配与控制,对各个功能模块分配时钟,并初始化各使能端信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

相关文章

-

2024-07-16

-

2024-07-11

-

2024-07-05

-

-

-

-

2024-05-21

-