FPGA实现时分多址的一种改进型方法

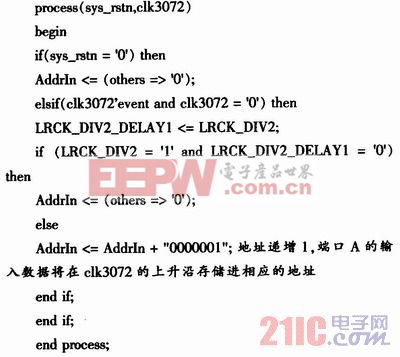

在端口A输入时钟clk3072的每个下降沿,端口A输入地址AddrIn都递增1,则在elk3072的上升沿,根据例化的双口RAM的IP核,端口A的四路输入数据将存储进相应的地址空间中。

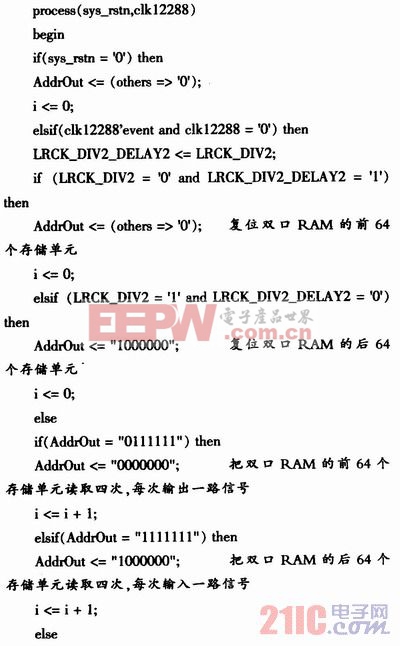

在端口B输入时钟elk12288的每个下降沿,端口B输入地址AddrOut都递增1,则在elk12288的上升沿,根据例化的双口RAM的IP核,相应的地址空间中的数据将通过Dout被读出来。

依次将输出数据以时分多址的帧格式传输出去。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码