数字中频正交采样及其FPGA实现

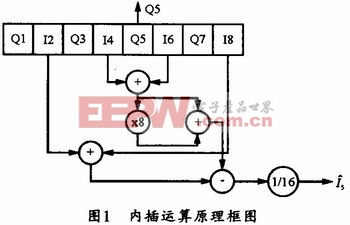

另外,由贝塞尔内插公式知,其8点中值公式为:

式中,I2、I4、I6、I8为已知点,

在实际应用中,考虑到FPGA的特性,可将

(8)式改写成以下形式:

这样,对于下列时间序列:Q1、I2、Q3、I4、Q5、I6、Q7、I8,按式(9)即可求出

2 基于FPGA的实现方案

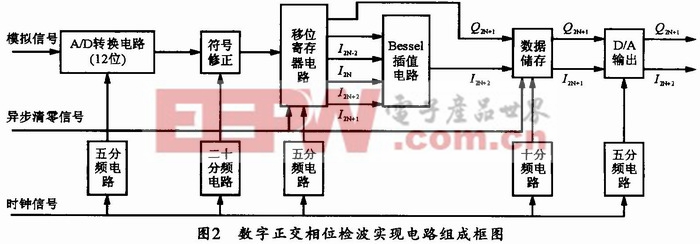

首先将输入FPGA的一路12位数字信号中的每一位都与时钟信号进行异或运算,以使I’(n)=x(2n)(-1)n和Q’(n)=x(2n+1)(-1)n+1,从而达到符号修正的目的。经过修正,输出的数字信号序列是一个由I的偶数项和Q的奇数项交替出现所组成的序列,即:I0,Q1,I2,Q3,I4,Q5,…,I2n,Q2n+1…。为实现Bessel插值,还需要得到某时刻Q2n+1值所对应的I的偶数项(I2n-2,I2n,I2n+2和I2n+4)。鉴于移位寄存器有延时功能,可使用12片移位寄存器74164取出I的偶数项序列,同时分离的还有相应的Q2n+1一路信号。接着,I的偶数项序列经过加法器电路进行有符号加、减法运算。由于Bessel插值中的分母均为2的整数幂,因而用右移来实现2的整数幂除法非常方便。其实现框图如图2所示。

该FPGA实现方法,由于只涉及移位、简单门和加减法运算,因此,用FPGA实现起来很方便,也可以获得较高的运算速率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码