基于VHDL的线性分组码编译码器设计

2.2 线性分组码译码器设计

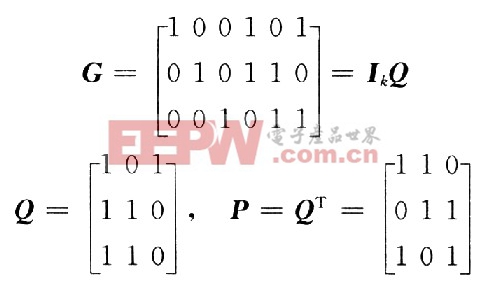

将生成矩阵G进行初等运算:原矩阵的第2,3,1行分别作为典型矩阵的第1,2,3行,可得典型生成矩阵:

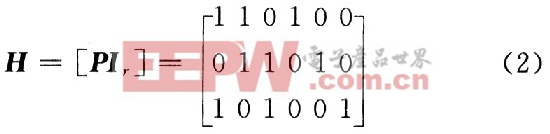

于是,典型监督矩阵H为:

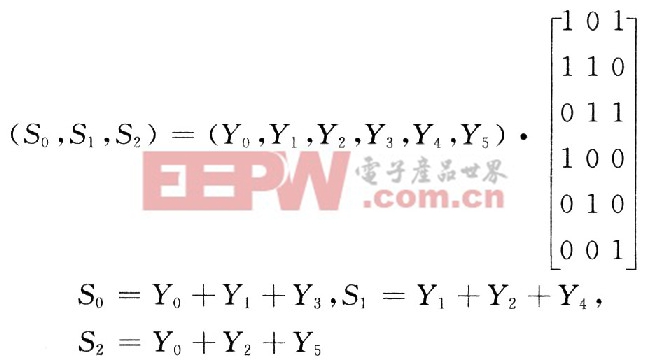

监督码元与信息码元之间的关系称为监督方程式(监督关系式),监督矩阵的每行中“1”的位置表示相应码元之间存在的监督关系,即下述三个监督方程:

发送的码字C=(C0,C1,…,Cn)。e表示传输中的差错;Y表示接收的码字。如果码字在传输过程中没有出现差错,则有HYT=HeT=O;出现差错时,则有

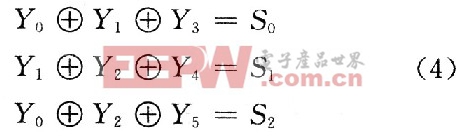

错误图样即校正子与错码位置的关系,因为r=3,所以有3个校正子,相应的有3个监督关系式。将式(3)改写为:

则可得由伴随子S决定对应的错误图样集e,即为典型监督矩阵的转置HT,如表1所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码