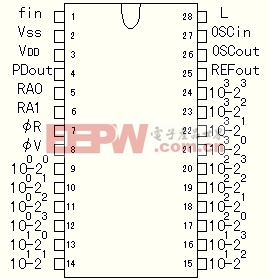

MC145163引脚图及引脚功能描述

MC145163是Motorola公司生产的锁相环芯片。图1所示的为MC145163P的特性与端子连接图.

图 1MC145163引脚图

MC145163引脚功能说明

MC145163P主要引脚功能说明 | |||

fin | 频率合成器的可程式化计数器(/N计数器部)的输入,通常fin 可以从VCO取得,以AC结合连接至1端子。在标准CMOS逻辑位准之大振幅信号的场合,也可以采用直接结合。 | ||

Vss | 电路的接地 | VDD(3端子) | 正电源(+5V) |

PDout | 当伯VCO控制信号,由相位比较器的3状态输出。 | ||

RA0 | 由这些输入,设定基准分频器(R计数器)的分频比。分频比可以从512,2048,4096中选择。 | ||

ΦR,ΦV | 利用这些相位比较器的输出,与通低频虑波器组合,成为VCO的控制信号。 | ||

BCD输入 | 这 些的输入数据,在N计数器的内容成为时,会被预先设定(preset). | ||

REFout | 内部基准振荡器外部基准信号的缓冲输出。 | ||

OSCout, OSCin(26端子,27端子) | 在这些端子上连接水晶振荡子时,便成为基准振荡器。使用适当值的电容连接OSCin与接地间,以及OSCout与接地间。OSCin也成为外部一产生基准信号的输入。这些信号通常在OSCin做AC结合。但是,在大振幅信号(CMOS逻辑位准)的组合,则使用DC结合。在外部基准Mode中,不必要与OSCout连接。 | ||

LD(28端子) | PLL锁栓检知信号,在PLL回路成为锁栓时(fr与fv的频率与相位为相同时)成为H,不成为锁栓时则产生脉波。 | ||