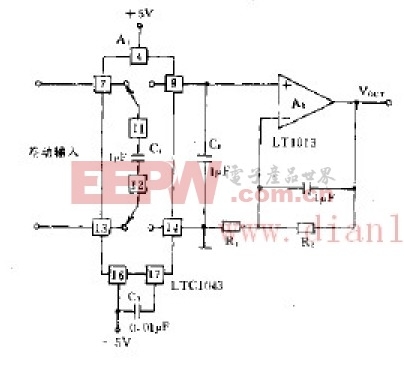

采用SCF的仪用放大器电路原理图

作者:dolphin

时间:2012-07-26

输入差信号频率应为时钟频率的一半以下,片内时钟电路产生的时钟频率由16与17脚接的电容C3所决定,当电容为0.01μF时,频率约为500Hz这时可得CMRR(共模抑制比)大于120dB。

如图所示,A2类似于反向输入放大器,曾以为1,A2采用LT1013时,其Vos=150μV,由于差信号加在LT1403的7,13脚,则同相输入电压范围最佳为+5V~-5V。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码