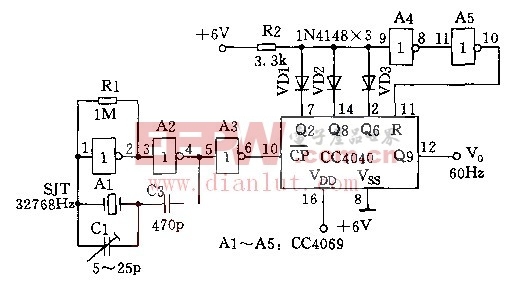

数字钟晶振时基原理及电路

作者:dolphin

时间:2012-07-23

本电路主要用作数字钟的时基振荡源,时基输出频率为60Hz,适用于LED数字钟集成电路,如LM8361一LM8365等。工作原理:如图所示电路是由12位二进制串行计数器/分配器CC4040和六反相器CC4069等构成的数字钟晶振时基电路。

电路中,CC4069的门A1和门A2构成振蔼频串为32768Hz的晶体振荡器。其输出经CC4069的门A3整形后送至CC4040的面端。本电路中,12位二进制串行计数器1分频器集成电路CC4040的输出端只用了Q2、Q6、Q8 、Q9,其它输出端可悬空。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码