基于FPGA的LCD显示远程更新

1 项目背景

1.1 研究背景

LCD显示屏的应用越来越广,数量越来越多。LCD显示屏应用广泛,无处不在。小到家庭各种电器设备,大到军事设备。更常见是用于各种公共场合如体育馆、广场等商业用途。给我们传递一种更为直观、生动的信息。从此我们的生活发生了巨大改变。巨大的应用巨大的市场带来了巨大的商机。传统的显示器大多采用控制系统与显示界面集成在一起的方案,不便于实时管理与有效维护,不便于及时更新;也不便于人亲临恶劣的工作环境下进行人为操控。LED显示屏用户迫切需要实现对LED显示屏的远程控制。

基于FPGA的LCD显示的远程更新是为了通过中央服务器可以实现有效地更新广泛分布的LCD显示屏,达到便于操纵,低成本,高效数据传输等特点。

1.2 基于FPGA的LCD显示的远程更新的优越性

本项目通过TCP/IP协议与远程控制进行通信,便且使用FTP协议来更新LCD显示内容。使中央服务器与分布在其他区域的LCD显示器组成网络并IP编址,可以通过中央服务器进行高效、方便、可靠地管理和维护LCD显示器。具有以下优势:

●采用可编程的FPGA进行设计,便于设计的更新与升级,节约成本。

●通过使用TCP/IP服务,使系统在传输数据和接受数据的过程中稳定性和可靠性得到有效地保证。

●采用SOPC集成系统的设计,是整个系统的复杂性大为降低。

●LCD体积小、质量轻、功耗低,可以用大规模集成电路直接驱动,可以在明亮环境下显示,不含射线伤害。

2 项目方案

2.1 实现功能

1、系统采用FPGA嵌入软核Microblaze作为微控制器,用于发送需要传输的数据。

2、通过TCP/IP协议有效地实现与远程LCD接收端进行通信。

3、在接收端,对收到的FTP数据进行存储并实现对LCD屏显示内容的更新。

2.2方案设计原理

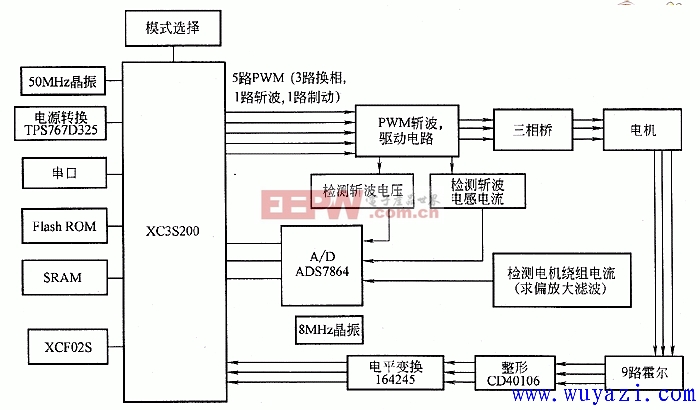

该方案使用Atlys Spartan®-6 FPGA 开发套件硬件平台,系统原理框图如下:

本方案做的是有线数据接收,首先使用FPGA嵌入软核Microblaze作为微控制器,然后通过TCP/IP协议与远程控制进行通信,在接受端接收到发送过来的信号,并存入RAM存储器中,同时对LCD显示屏进行更新。

2.3硬件设计

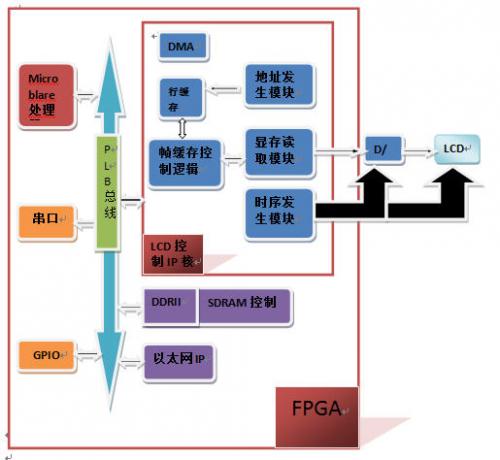

通过上面对整个系统功能要求, 性能要求的分析, 我们可以确定系统的基本硬件结构, 其组成框图如下所示:

从上面的系统硬件框图中我们可以看到,整个系统由Microblaze组成的微控制器,PLB外设总线,LCD控制器,以太网、以及片上RAM等组成。Microblaze微控制器作为控制器,通过PLB总线与各部分控制器以及外围联接,负责整个系统的运行。片上SDRAM作为Microblaze微控制器执行指令的存储空间,在LCD更新过程中也需要保存接收到的FTP数据。整个系统主要就是LCD控制IP核以及以太网通信部分。

LCD控制IP核主要由地址发生模块、显存读取模块、时序发生模块、帧存控制模块、行缓存等模块组成。

·地址发生模块

地址发生模块为显存读取模块提供了一张显存地址表,地址表上涵盖了LCD上每个像素点的访问地址,地址发生模块设计保证在LCD显示扫描时钟进行到某一像素点时,恰好向显存读取模块提供该像素点的地址,显存读取模块据此地址从显存读取相应的像素点信息。地址发生模块动态地向显存读取模块提供地址的行为与显存读取模块的读操作是同步进行的,同步时钟为像素点时钟D-CLK,触发信号是来自时序发生模块的数据使能信号Data-EN,复位信号为时序发生模块的场同步消隐信号HB。

·显存读取模块

显示读取子模块通过16 bit并行数据总线访问显存SRAM,对FPGA“调色板”颜色处理子模块提供4 bit并行数据接口。本模块的输入时钟频率是LCD像素点时钟信号D-CLK的4倍,触发信号为LCD数据使能信号Data-EN,每4 bit显存内容描述一个像素点,可显示16种颜色(颜色及色深可根据系统的要求,适时扩充)。显存读取状态机循环1次可读取4个像素点的信息,在时钟信号的触发下,依次将点像素信息输送至“调色板”颜色处理子模块。将以上操作分解为如下步骤:(1)消隐:每行或每场的非显示阶段,此阶段送至LCD的图像信息无效;(2)SO:取每包图像信息的第1个像素点信息,并送至“调色板”颜色处理子模块;(3)s1:取每包图像信息的第2个像素点信息,并送至“调色板”颜色处理子模块;(4)S2:取每包图像信息的第3个像素点信息,并送至“调色板”颜色处理子模块;(5)s3:取每包图像信息的第4个像素点信息,并送至“调色板”颜色处理子模块。

·时序发生模块

时序发生模块主要产生数字TFT-LCD所需的像素点时钟D-CLK、行同步信号H-SYNC、场同步信号V-SYNC、行同步信号H-SYNC、数据使能信号Data-EN信号。随着FPGA的出现,利用编程逻辑方法产生行场扫描时序是一个发展方向。这种方法具有电路简单、功能强、修改方便、可靠性高等优点,只需在代码中修改一些时序参数就能产生任意时序的波形,可以支持各种接口时序要求的TFT. - LCD显示器。

·帧存控制模块

帧存控制模块实现2个帧存SRAM的“乒乓”切换,当DSP向其中一个帧存写显示信息时,由FPGA构成的帧存控制模块将另一个帧存的控制权交给LCD显示控制器图像处理模块,反之亦然。

·软件设计

TCP/IP是一种网络通信协议,它规范了网络上所有通信设备,尤其是一个主机与另一个主机之间的数据往来格式及传送方式。TCP/IP是Internet的基础协议,也是一种计算机数据打包和寻址的标准方法。在Intemet中几乎可以无差错地传送数据。

LWIP是瑞士计算机科学院的Adam Dunkels等开发的一套用于嵌入式系统的开放源代码TCP/IP协议栈。LWIP既可以移植到操作系统上,也可以在无操作系统的情况下独立运行。LWIP TCP/IP实现的重点是在保持TCP协议主要功能的基础上减少对RAM的占用,一般它只需要几十kB的RAM和50 kB左右的ROM就可以运行,使得LWIP协议栈适合在嵌入式系统中使用。

LWIP的特性如下:

(1)支持多网络接口下的IP转发;

(2)支持ICMP协议;

(3)包括实验性扩展的的UDP(用户数据报协议);

(4)包括阻塞控制,I T估算,以及快速恢复和转发的TCP(传输控制协议);

(5)提供专门的内部回调接口(Raw API)用于提高应用程序性能;

(6)可选择的Berkeley接121API(多线程情况下);

(7)在的版本中支持PPP;

(8)新版本中增加了的IP fragment的支持;

(9)支持DHCP协议,动态分配IP地址。

在Xilinx的Spartan 6 FPGA上实现的LWIP TCP/IP采用的是LWIP的版本V1.1.1,提出和采用以下几种移植和运行方式:

(1 )TCP/IP协议的每一层是一个单独进程,链路层是一个进程,IP层是一个进程,TCP层是一个进程。这样的优势是网络协议的每一层都非常清晰,代码的调试和理解都非常容易;的缺点是数据跨层传递时会引起上下文切换。接收一个TCP信息段要引起3次上下文切换(从网卡驱动程序到链路层进程,从链路层进程到IP层进程,从IP层进程~]TCP进程)。对于操作系统来说,任务切换是要浪费时间的。过频的上下文切换使得系统运行比较沉重,这是不可取的。

(2) TCP/IP协议栈在操作系统内核当中,应用程序通过操作系统的系统调用和协议栈来进行通讯,这样TCP/IP的协议栈就限定于特定的操作系统内核了。此法理论上可以实现,但代码不具有通用性,不便于将来的维护和再移植,同样也是不太可取的。

(3)TCP/IP协议栈都在一个进程当中,这样TCP/IP协议栈就和操作系统内核分开了,而应用层程序既可以是单独的进程也可以驻留在TCP/IP进程中。如果应用程序是单独的进程,可以通过操作系统的邮箱、消息队列等和TCP/IP进程进行通讯。此种方式移植层次清晰,移植代码量适中,是比较好的思路,并且在此基础上移植调试成功,证明此思路是切实可行的,但缺点是依赖于操作系统的任务通信机制,不能得到很高的性能。

(4)把应用层程序驻留TCP/IP进程中,则应用层程序就利用内部回调函数口(Raw API)和TCP/IP协议栈通讯。应用层程序既可以是独立的任务,也可以在TCP/IP线程中利用内部回调函数n(Raw API)和TCP/IP协议栈通讯。此方式不依赖实时操作系统,能在无操作系统的情况下运行。经过对LWIP协议栈源码的彻底消化,改写其接口代码,经多次调试移植成功,测试性能得到了很大提升。

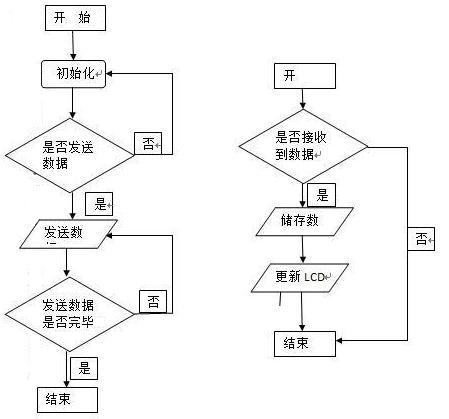

2.4 软件设计流程图

软件设计分为发送部分和接受部分。

程序流程图如下:

发送端流程图 接收端流程图

关键词: FPGA

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码