74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)

74LS161功能介绍

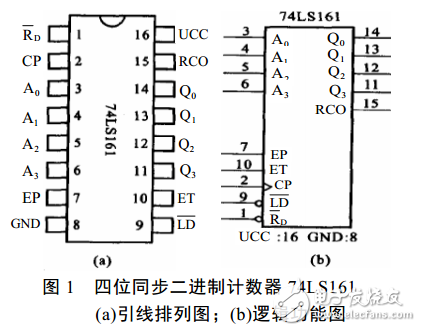

74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端,可以串接计数器使用。

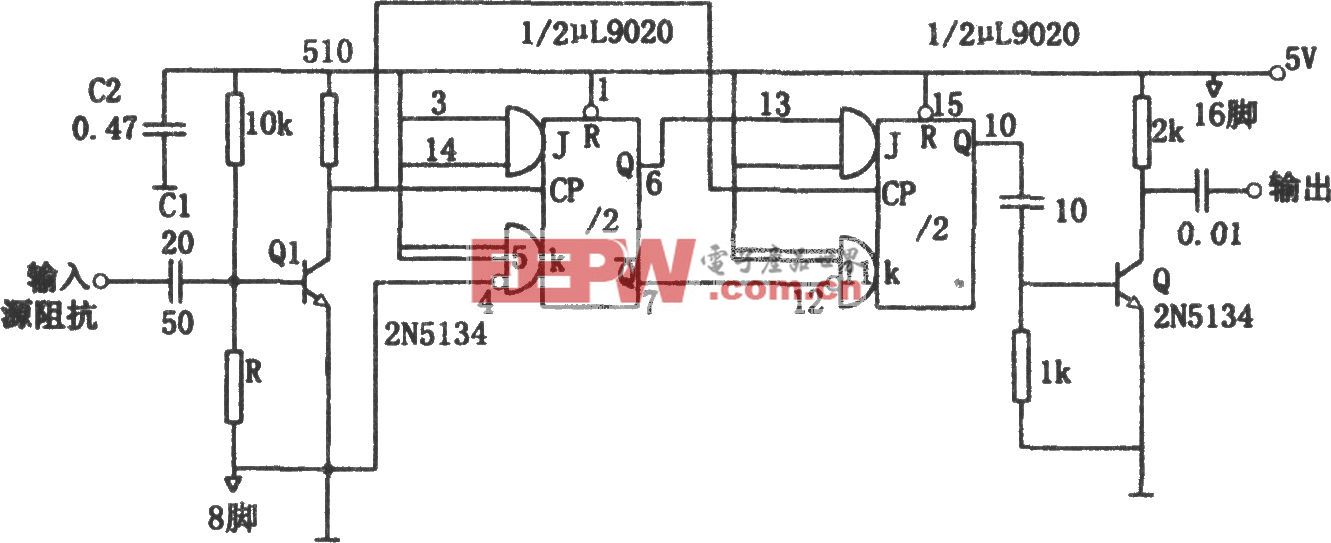

74LS161的引脚排列和逻辑功能如图1所示。各引出端的逻辑功能如下。1脚为清零端/RD,低电平有效。2脚为时钟脉冲输入端CP,上升沿有效(CP↑)。3~6脚为数据输入端A0~A3,可预置任意四位二进制数。7脚和10脚分别为计数控制端EP和ET,当其中有一脚为低电平时计数器保持状态不变,当均为高电平时为计数状态。9脚为同步并行置数控制端/LD,低电平有效。11~14脚为数据输出端QQ30~。15脚为进位输出端RCO,高电平有效。74LS161可编程度数器的真值表如下。

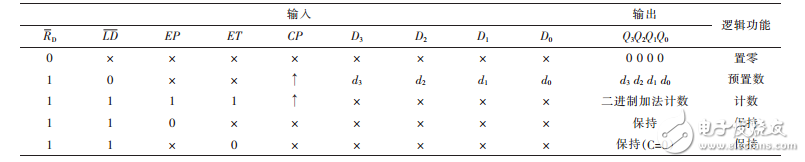

表 74LS161可编程度数器的真值表

一、74LS161集成计数器电路(十进制计数器)

单片161可以实现16以内任意进制的加法计数功能。实现途径有清零法和置数法两种。以实现十进制加法计数器为例:

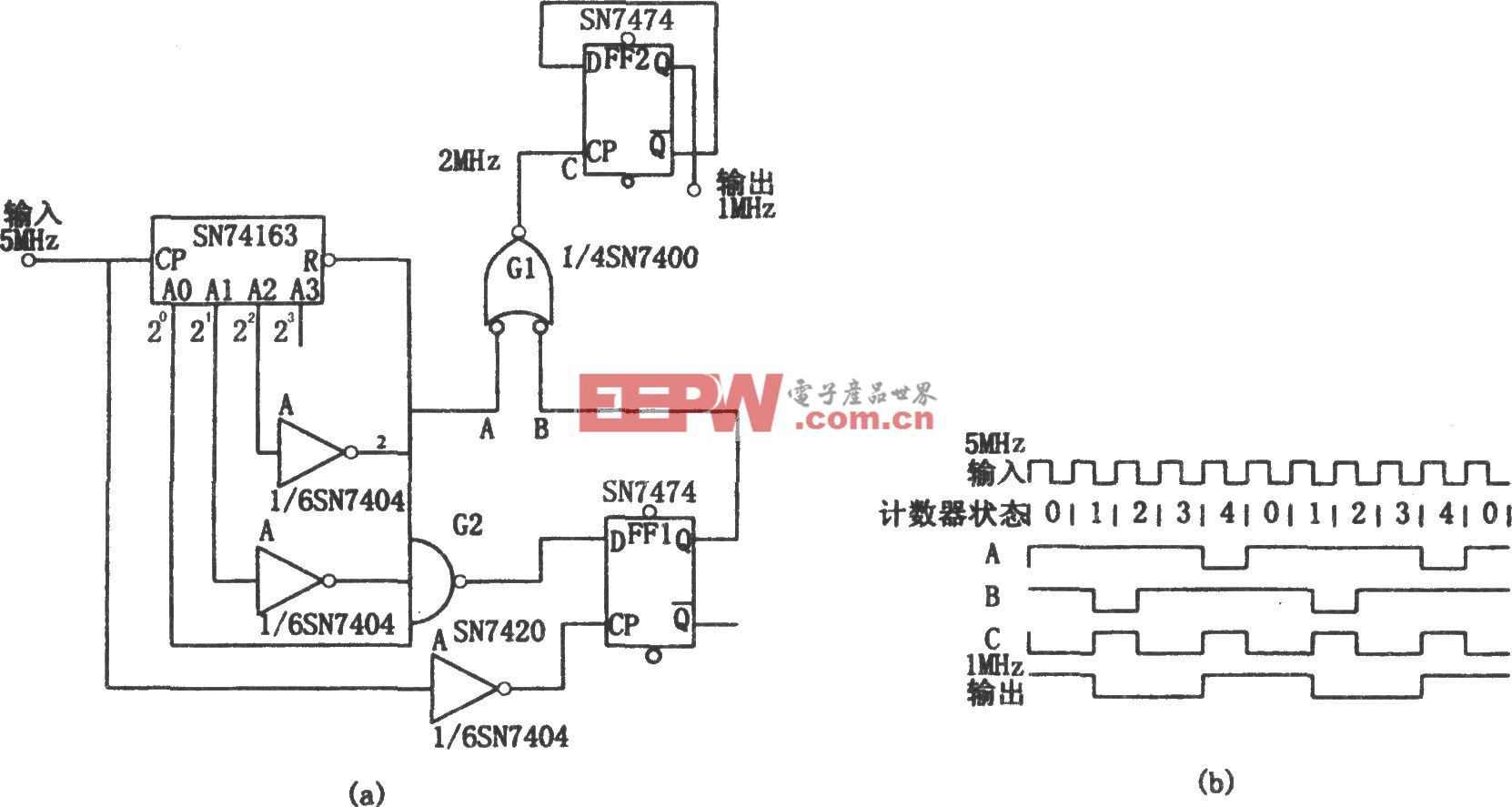

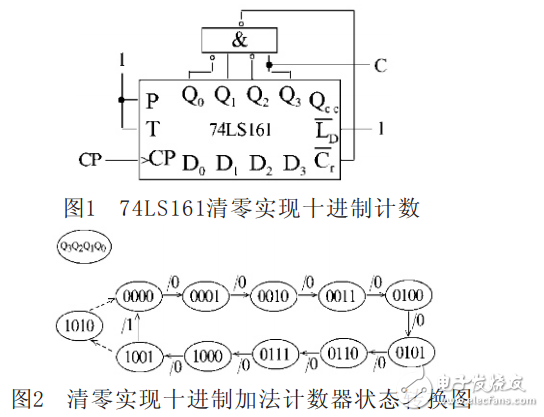

1)161的是异步清零端。当Q3Q2Q1Q0=1010(即10)状态时,通过译码电路给出低电平信号,将计数器清零回到0000状态。电路图和状态转换图如图1,图2所示。

由于置零信号随着计数器被置零而立即消失,所以置零信号持续时间极短,可能触发器还未来得及复位,置零信号已经消失,导致电路的误动作。因此,这种电路的可靠性不高。为了克服这个缺点,时常在译码电路和之间加一个SR锁存器,延长置零信号的宽度,从而增加电路的可靠性。

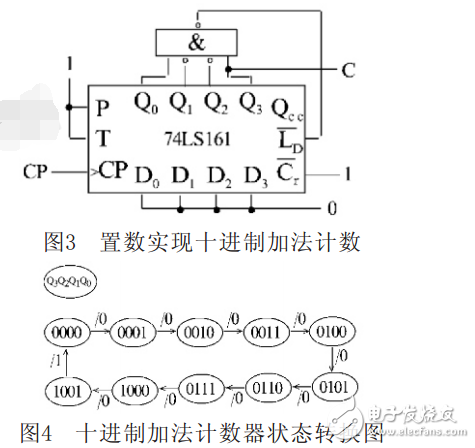

2)161的是同步置数置数端,可以用置数法实现十进制加法计数功能。161共有16个状态,采用置数法实现十进制加法计数功能时只要跳过其中任意6个状态就可以,方法有很多,这里仅举一种。当Q3Q2Q1Q0=1001(即9)状态时,通过译码电路给出低电平信号,将计数器置0回到0000状态。电路图和状态转换图如图3,图4所示。

由于161的置数是同步式的,所以不存在异步置零法中因置零信号持续时间过短而可靠性不高的问题。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码